Architektura systemu wieloprocesorowego

System wieloprocesorowy definiuje się jako „system z więcej niż jednym procesorem”, a dokładniej „liczbą jednostek centralnych połączonych ze sobą w celu umożliwienia przetwarzania równoległego”.

Głównym celem multiprocesora jest zwiększenie szybkości wykonywania systemu. Inne cele to odporność na awarie i dopasowanie aplikacji.

Termin „wieloprocesorowy” można pomylić z terminem „ wieloprocesorowy ”. Podczas gdy przetwarzanie wieloprocesorowe to rodzaj przetwarzania, w którym dwa lub więcej procesorów współpracuje ze sobą w celu jednoczesnego wykonywania wielu programów, wieloprocesorowość odnosi się do architektury sprzętowej, która umożliwia przetwarzanie wieloprocesorowe.

Systemy wieloprocesorowe są klasyfikowane według sposobu obsługi dostępu do pamięci procesora oraz tego, czy procesory systemowe są jednego typu, czy różnych.

Typy systemów wieloprocesorowych

Istnieje wiele rodzajów systemów wieloprocesorowych:

- Luźno powiązany system wieloprocesorowy

- Ściśle sprzężony system wieloprocesorowy

- Homogeniczny system wieloprocesorowy

- Heterogeniczny system wieloprocesorowy

- System wieloprocesorowy z pamięcią współdzieloną

- System wieloprocesorowy z pamięcią rozproszoną

- System jednolitego dostępu do pamięci (UMA).

- system cc-NUMA

- System hybrydowy – współdzielona pamięć systemowa dla danych globalnych i pamięć lokalna dla danych lokalnych

Luźno sprzężony (pamięć rozproszona) system wieloprocesorowy

W luźno sprzężonych systemach wieloprocesorowych każdy procesor ma własną pamięć lokalną, kanały wejścia/wyjścia (I/O) i system operacyjny . Procesory wymieniają dane przez szybką sieć komunikacyjną, wysyłając wiadomości za pomocą techniki znanej jako „ przekazywanie wiadomości ”. Luźno sprzężone systemy wieloprocesorowe są również znane jako systemy z pamięcią rozproszoną, ponieważ procesory nie współdzielą pamięci fizycznej i mają indywidualne kanały we/wy.

Charakterystyka systemu

- Systemy te są w stanie wykonywać programowanie z wieloma instrukcjami na wielu danych (MIMD).

- Ten typ architektury umożliwia przetwarzanie równoległe .

- Pamięć rozproszona jest wysoce skalowalna.

System wieloprocesorowy ze współdzieloną pamięcią ściśle połączoną z procesorami.

Symetryczny system wieloprocesorowy to system ze scentralizowaną pamięcią współdzieloną zwaną pamięcią główną (MM), działający w ramach jednego systemu operacyjnego z dwoma lub większą liczbą jednorodnych procesorów.

Istnieją dwa rodzaje systemów:

- Jednolity system dostępu do pamięci (UMA).

- system NUMA

System jednolitego dostępu do pamięci (UMA).

- Heterogeniczny system wieloprocesorowy

- Symetryczny system wieloprocesorowy (SMP)

Heterogeniczny system wieloprocesorowy

Heterogeniczny system wieloprocesorowy zawiera wiele, ale nie jednorodnych jednostek przetwarzających — jednostki centralne (CPU), jednostki przetwarzania grafiki (GPU), cyfrowe procesory sygnałowe (DSP) lub dowolny typ układów scalonych specyficznych dla aplikacji (ASIC). Architektura systemu pozwala dowolnemu akceleratorowi — na przykład procesorowi graficznemu — działać na tym samym poziomie przetwarzania, co procesor systemowy.

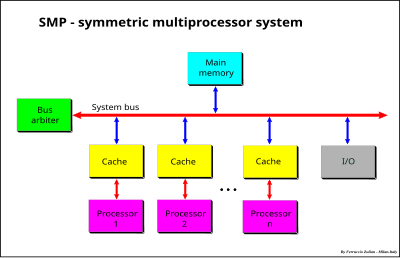

Symetryczny system wieloprocesorowy

Systemy działające w ramach jednego systemu operacyjnego ( systemu operacyjnego ) z dwoma lub większą liczbą jednorodnych procesorów i ze scentralizowaną wspólną pamięcią główną.

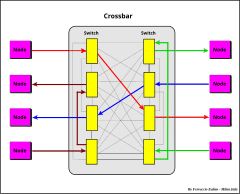

Symetryczny system wieloprocesorowy (SMP) to system z pulą jednorodnych procesorów działający pod jednym systemem operacyjnym ze scentralizowaną, współdzieloną pamięcią główną. Każdy procesor, wykonujący różne programy i pracujący na różnych zestawach danych, ma możliwość współdzielenia wspólnych zasobów (pamięć, urządzenie wejścia/wyjścia, system przerwań itd.), które są połączone za pomocą magistrali systemowej, krzyżaka lub miksu z tych dwóch lub szynę adresową i poprzeczkę danych.

Każdy procesor ma własną pamięć podręczną, która działa jako pomost między procesorem a pamięcią główną. Funkcja pamięci podręcznej polega na zmniejszeniu potrzeby dostępu do danych w pamięci głównej, zmniejszając w ten sposób ruch na magistrali systemowej.

Wykorzystanie pamięci współdzielonej pozwala na uzyskanie jednolitego czasu dostępu do pamięci (UMA).

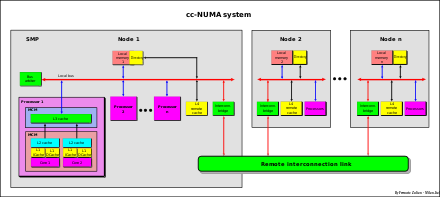

system cc-NUMA

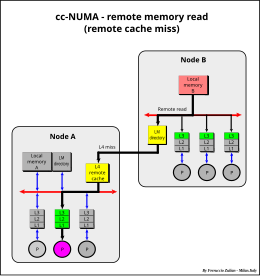

Wiadomo, że system SMP ma ograniczoną skalowalność. Aby przezwyciężyć to ograniczenie, zwykle używana jest architektura zwana „cc-NUMA” (spójność pamięci podręcznej - niejednolity dostęp do pamięci). Główną cechą systemu cc-NUMA jest współdzielona pamięć globalna, która jest dystrybuowana do każdego węzła, chociaż efektywny „dostęp” procesora do pamięci zdalnego podsystemu komponentów lub „węzła” jest wolniejszy w porównaniu z pamięcią lokalną dostęp, dlatego dostęp do pamięci jest „niejednolity”.

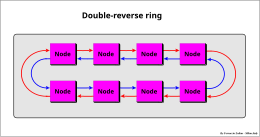

System cc-NUMA to klaster systemów SMP – każdy nazywany „węzłem”, który może mieć pojedynczy procesor, procesor wielordzeniowy lub połączenie tych dwóch, jednego lub innego rodzaju architektury – połączonych przez szybka „sieć połączeń”, która może być „łączem”, które może być pojedynczym lub podwójnym pierścieniem zwrotnym lub wielopierścieniowymi, połączeniami punkt-punkt lub ich mieszanką (np. IBM Power Systems) , magistrala połączenia międzysieciowe (np. NUMAq), „crossbar”, „segmented bus” ( NUMA Bull HN ISI ex Honeywell ), „ router siatkowy ” itp.

cc-NUMA jest również nazywany architekturą „rozproszonej pamięci współdzielonej” (DSM).

Różnica w czasach dostępu między pamięcią lokalną i zdalną może być również rzędu wielkości, w zależności od rodzaju zastosowanej sieci połączeń (szybciej w przypadku magistrali segmentowej, typu crossbar i połączenia punkt-punkt; wolniej w przypadku połączenia szeregowego).

Przykłady połączeń

zwykle używana jest duża zdalna pamięć podręczna (patrz Zdalna pamięć podręczna ). Dzięki takiemu rozwiązaniu system cc-NUMA bardzo zbliża się do dużego systemu SMP.

Architektura ściśle powiązana kontra luźno powiązana

Obie architektury mają kompromisy, które można podsumować w następujący sposób:

- Luźno powiązane architektury charakteryzują się wysoką wydajnością każdego pojedynczego procesora, ale nie umożliwiają łatwego równoważenia obciążenia między procesorami w czasie rzeczywistym.

- Ściśle powiązane architektury charakteryzują się łatwym równoważeniem obciążenia i dystrybucją między procesorami, ale cierpią z powodu wąskiego gardła polegającego na współdzieleniu wspólnych zasobów przez jedną lub więcej magistrali.

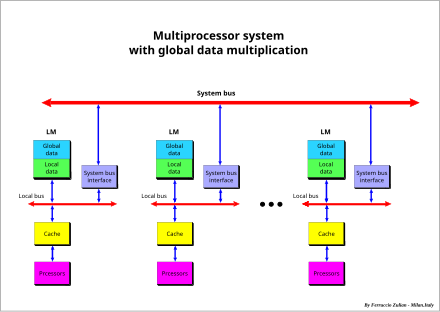

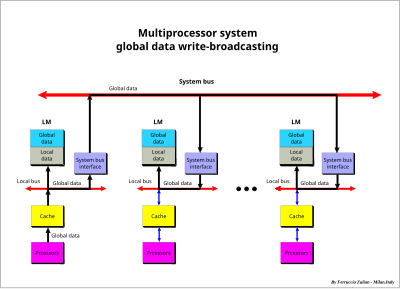

System wieloprocesorowy z możliwością globalnego powielania danych

Podejście pośrednie, pomiędzy tymi z dwóch poprzednich architektur, polega na posiadaniu wspólnych zasobów i zasobów lokalnych, takich jak pamięć lokalna (LM) w każdym procesorze.

Wspólne zasoby są dostępne ze wszystkich procesorów za pośrednictwem magistrali systemowej, podczas gdy zasoby lokalne są dostępne tylko dla lokalnego procesora. Pamięci podręczne można rozpatrywać w tej perspektywie jako pamięci lokalne.

Ten system (opatentowany przez F. Zulian ), używany w systemie opartym na DPX/2 300 Unix (Bull Hn Information Systems Italia (ex Honeywell)), jest mieszanką ściśle i luźno powiązanych systemów i wykorzystuje wszystkie postępy tych dwie architektury.

Pamięć lokalna jest podzielona na dwa sektory, dane globalne (GD) i dane lokalne (LD).

Podstawową koncepcją tej architektury jest posiadanie globalnych danych, które są modyfikowalnymi informacjami, dostępnymi dla wszystkich procesorów. Informacje te są powielane i przechowywane w każdej pamięci lokalnej każdego procesora.

Za każdym razem, gdy dane globalne są modyfikowane w pamięci lokalnej, do magistrali systemowej do wszystkich innych pamięci lokalnych wysyłane jest sprzętowe rozgłaszanie zapisu i rozgłaszania, aby zachować globalną spójność danych. W ten sposób dane globalne mogą być odczytywane przez każdy procesor uzyskujący dostęp do własnej pamięci lokalnej bez angażowania magistrali systemowej. Dostęp do magistrali systemowej jest wymagany tylko wtedy, gdy dane globalne są modyfikowane w pamięci lokalnej w celu aktualizacji kopii tych danych przechowywanych w innych pamięciach lokalnych.

Lokalne dane mogą być wymieniane w luźno powiązanym systemie poprzez przesyłanie komunikatów