WD16

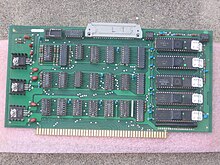

Mikroprocesor WD16 w pięciu 40-stykowych obudowach zainstalowany na płycie procesora Alpha Microsystems AM-100, która łączy się z magistralą S-100 .

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | 1976 |

| Wspólni producenci | |

| Wydajność | |

| Maks. Częstotliwość taktowania procesora | do 3,3 MHz |

| Szerokość danych | 16 |

| Szerokość adresu | 16 |

| Architektura i klasyfikacja | |

| Zestaw instrukcji | PDP-11 jak |

| Instrukcje | 119 |

| Specyfikacje fizyczne | |

| pakiet(y) |

|

| Historia | |

| Następca | nic |

WD16 to 16-bitowy mikroprocesor wprowadzony przez firmę Western Digital w październiku 1976 r. Jest oparty na chipsecie MCP-1600 , który stanowił podstawę niskobudżetowego minikomputera DEC LSI -11 oraz procesora Pascal MicroEngine zaprojektowanego specjalnie do obsługi UCSD p-System wydajnie. Każdy używał innego mikrokodu. WD16 implementuje rozszerzenie architektury zestawu instrukcji PDP-11, ale nie jest kodem maszynowym kompatybilny z PDP-11. Zestaw instrukcji i mikrokodowanie zostały stworzone przez Dicka Wilcoxa i Richa Notariego. WD16 jest przykładem ortogonalnej architektury CISC . Większość instrukcji dwuargumentowych może działać z pamięcią do pamięci w dowolnym trybie adresowania, a niektóre instrukcje mogą skutkować nawet dziesięcioma dostępami do pamięci.

WD16 jest zaimplementowany w pięciu 40-pinowych pakietach DIP . Maksymalna częstotliwość taktowania wynosi 3,3 MHz. Jego interfejs do pamięci odbywa się za pośrednictwem 16-bitowej multipleksowanej szyny danych/adresowej.

WD16 jest najbardziej znany z zastosowania w płytach procesorów Alpha Microsystems AM-100 i AM-100/T. Prototyp został zademonstrowany w 1977 roku. Od 1981 roku było co najmniej 5000 komputerów Alpha Micro opartych na WD16. Jeszcze w 1982 r. Alpha Micro oparte na WD16 nadal były określane jako „supermikro”. WD16 został zastąpiony przez Motorolę 68000 w czerwcu 1982 roku.

Pamięć

Formaty danych

Najmniejszą jednostką adresowalnej i zapisywalnej pamięci jest 8-bitowy bajt . Bajty mogą być również przechowywane w dolnej połowie rejestrów od R0 do R5.

16-bitowe słowa są przechowywane w postaci little-endian z najmniej znaczącymi bajtami pod niższym adresem. Słowa są zawsze wyrównane do parzystych adresów pamięci. Słowa mogą być przechowywane w rejestrach od R0 do R7.

32-bitowe podwójne słowa mogą być przechowywane tylko w parach rejestrów, przy czym niższe słowo jest przechowywane w rejestrze o niższym numerze. Wartości 32-bitowe są używane przez MUL, DIV oraz niektóre instrukcje obracania i przesunięcia arytmetycznego.

zmiennoprzecinkowe mają długość 48 bitów i mogą być przechowywane tylko w pamięci. Ten format jest w połowie drogi między formatami zmiennoprzecinkowymi o pojedynczej i podwójnej precyzji. Są one przechowywane w nietypowym mid-endian, czasami określanym jako „PDP-endian”. Wartości zmiennoprzecinkowe są zawsze wyrównywane do parzystych adresów. Pierwsze słowo zawiera znak, wykładnik i starszy bajt mantysy. Następny wyższy adres zawiera dwa środkowe bajty mantysy, a następny wyższy adres zawiera dwa najniższe bajty mantysy. Pełny format jest następujący:

1. Znak 1-bitowy dla całej liczby, który jest równy zero dla wartości dodatniej.

2. 8-bitowy wykładnik o podstawie dwójki w notacji przekraczającej 128 z zakresem +127, -128. Jedyną legalną liczbą z wykładnikiem równym -128 jest prawdziwe zero (same zera).

3. 40-bitowa mantysa z implikowanym MSB.

| 15 | 14 | 7 | 6 | 0 | ||||||||||||

| Adres+0 | S | Wykładnik potęgowy | Mantysa (wysoka) | |||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Adres+2 | Mantysa | (środek) | ||||||||||||||

| 15 | 8 | 7 | 0 | |||||||||||||

| Adres+4 | Mantysa | (Niski) | ||||||||||||||

Zarządzanie pamięcią

16-bitowe adresy WD16 mogą bezpośrednio uzyskiwać dostęp do 64 KB pamięci. WD16 nie oferuje żadnego wewnętrznego zarządzania ani ochrony pamięci. W aplikacji AM-100 ostatnie 256 lokalizacji pamięci jest mapowanych na przestrzeń portu . Ponieważ większość komputerów AM-100 była używana jako komputery dla wielu użytkowników, pamięć była zwykle rozszerzana powyżej 64 KB przy przełączaniu banków . Chociaż AM-100 można skonfigurować dla maksymalnie 22 użytkowników i 512 kilobajtów pamięci RAM, typowa konfiguracja pamięci dla AM-100 dla 9 użytkowników może mieścić się w zakresie 352 kilobajtów. W 1981 roku do AM-100/T zaoferowano opcjonalną jednostkę zarządzania pamięcią AM-700, która umożliwiła segmentacja pamięci w krokach co 256 bajtów.

Rejestry procesora

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Procesor zawiera osiem 16-bitowych rejestrów ogólnego przeznaczenia , od R0 do R7. Rejestry mogą być używane do dowolnych celów z następującymi wyjątkami: Rejestr R7 jest licznikiem programu (PC). Chociaż każdy rejestr może być użyty jako wskaźnik stosu, R6 jest wskaźnikiem stosu (SP) używanym do przerwań sprzętowych i pułapek. R0 to liczba instrukcji transferu bloku.

Tryby adresowania

Większość instrukcji przydziela sześć bitów do określenia każdego operandu. Trzy bity wybierają jeden z ośmiu trybów adresowania, a trzy bity wybierają rejestr ogólny. Kodowanie trybu adresowania operandu sześciobitowego jest następujące:

| 5 | 3 | 2 | 0 | ||

| Tryb | Rejestr | ||||

W poniższych sekcjach każdy element zawiera przykład zapisu operandu w asemblerze. Rn oznacza jeden z ośmiu rejestrów, zapisanych od R0 do R7.

Ogólne tryby adresowania rejestrów

Poniższe osiem trybów można zastosować do dowolnego rejestru ogólnego. Ich efekty po zastosowaniu do R6 (wskaźnik stosu, SP) i R7 (licznik programu, PC) są omówione oddzielnie w poniższych sekcjach.

| Kod | Nazwa | Przykład | Opis |

|---|---|---|---|

| 0n | Rejestr | Rn | Operand jest w Rn |

| 1n | Rejestracja odroczona | (Rn) | Rn zawiera adres operandu |

| 2n | Automatyczne zwiększanie | (Rn)+ | Rn zawiera adres operandu, a następnie inkrementuje Rn |

| 3n | Autoinkrementacja odroczona | @(Rn)+ | Rn zawiera adres adresu operandu, następnie zwiększ Rn o 2 |

| 4n | Automatyczne zmniejszanie | −(Rn) | Zmniejsz Rn, a następnie użyj wyniku jako adresu operandu |

| 5n | Automatyczne zmniejszanie odroczone | @−(Rn) | Zmniejsz Rn o 2, a następnie użyj wyniku jako adresu adresu operandu |

| 6n | Indeks | X(Rn) | Rn+X to adres operandu |

| 7n | Indeks odroczony | @X(Rn) | Rn+X to adres adresu operandu |

W trybach indeksu i indeksu odroczonego X jest wartością 16-bitową pobraną z drugiego słowa instrukcji. W instrukcjach dwuargumentowych oba operandy mogą używać tych trybów. Takie instrukcje mają długość trzech słów.

Operacje autoinkrementacji i autodekrementacji w rejestrze są wykonywane o 1 w instrukcjach bajtowych, o 2 w instrukcjach słownych io 2, gdy używany jest tryb odroczony, ponieważ ilość, do której adresowany jest rejestr, jest wskaźnikiem (słowem).

Zaprogramuj tryby adresowania liczników

Po określeniu R7 (licznik programu) cztery tryby adresowania naturalnie dają użyteczne efekty:

| Kod | Nazwa | Przykład | Opis |

|---|---|---|---|

| 27 | Natychmiastowy | #N | Operand jest kolejnym słowem instrukcji |

| 37 | Absolutny | @#A | Adres operandu jest następnym słowem instrukcji |

| 67 | Względny | A | Adres operandu jest kolejnym słowem instrukcji dodanej do PC |

| 77 | Względny odroczony | @A | Adres adresu argumentu jest kolejnym słowem instrukcji dodanej do PC |

Istnieją tylko dwa typowe zastosowania trybu bezwzględnego, którego składnia łączy tryb natychmiastowy i odroczony. Pierwszym z nich jest dostęp do zarezerwowanych lokalizacji procesora pod adresem 0000-003F. Drugim jest określenie rejestrów wejścia/wyjścia w przestrzeni portu, ponieważ rejestry dla każdego urządzenia mają określone adresy pamięci. Tryb względny ma prostszą składnię i jest bardziej typowy dla odwoływania się do zmiennych programu i miejsc docelowych skoków. Program, który używa trybu względnego (i względnego trybu odroczonego) wyłącznie dla odniesień wewnętrznych, jest niezależny od pozycji ; nie zawiera żadnych założeń dotyczących jego własnej lokalizacji, więc można go załadować do dowolnej lokalizacji w pamięci, a nawet przenieść, bez potrzeby dostosowywania jego adresów w celu odzwierciedlenia jego lokalizacji. Przy obliczaniu takich adresów w stosunku do bieżącej lokalizacji procesor wykonuje relokację w locie.

Tryby natychmiastowy i bezwzględny to odpowiednio tryb automatycznego przyrostu i odroczony tryb automatycznego przyrostu, stosowane na komputerze PC. Gdy słowo pomocnicze znajduje się w instrukcji, PC dla następnej instrukcji jest automatycznie zwiększany za słowem pomocniczym. Ponieważ PC zawsze wskazuje na słowa, operacja automatycznego zwiększania odbywa się zawsze o krok 2.

Tryby adresowania stosu

R6, również pisany jako SP, jest używany jako stos sprzętowy dla pułapek i przerwań. Konwencja wymuszona przez zestaw trybów adresowania zapewnianych przez WD16 polega na tym, że stos rośnie w dół — w kierunku niższych adresów — w miarę wypychania na niego elementów. Gdy tryb jest zastosowany do SP lub do dowolnego rejestru, którego programista zdecyduje się użyć jako stosu oprogramowania, tryby adresowania mają następujące skutki:

| Kod | Nazwa | Przykład | Opis |

|---|---|---|---|

| 16 | Odroczony | (SP) | Operand znajduje się na szczycie stosu |

| 26 | Automatyczne zwiększanie | (SP)+ | Operand znajduje się na szczycie stosu, a następnie zdejmij go |

| 36 | Autoinkrementacja odroczona | @(SP)+ | Wskaźnik do operandu znajduje się na górze stosu; wysuń wskaźnik |

| 46 | Automatyczne zmniejszanie | −(SP) | Przenieś wartość na stos |

| 66 | Indeksowane | X(SP) | Operand znajduje się w odległości X od wierzchołka stosu |

| 76 | Indeksowane odroczone | @X(SP) | Wskaźnik do operandu znajduje się w odległości X od wierzchołka stosu |

Chociaż stosy oprogramowania mogą zawierać bajty, SP zawsze wskazuje na stos słów. Operacje autoinkrementacji i autodekrementacji na SP są zawsze o krok 2.

Zestaw instrukcji

Większość instrukcji WD16 operuje na bajtach i słowach. Bajty są określane przez numer rejestru - identyfikujący bajt niższego rzędu w rejestrze - lub przez lokalizację pamięci. Słowa są określone przez numer rejestru lub lokalizację pamięci bajtu niższego rzędu, który musi być liczbą parzystą. Na listach w następnych sekcjach litera B jest dodawana do symbolu instrukcji w celu określenia operacji na bajtach, na przykład MOV staje się MOVB. Wszystkie kody operacyjne i adresy są wyrażone w systemie szesnastkowym .

Instrukcje dwuargumentowe

bity wyższego rzędu określają operację, która ma zostać wykonana. Dwie grupy po sześć bitów określają tryb adresowania argumentu źródłowego i tryb adresowania argumentu docelowego, jak zdefiniowano powyżej.

| 15 | 12 | 11 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||

| Kod operacji | Src | Rejestr | Cel | Rejestr | |||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 1000 | DODAĆ | Dodaj: Dest ← Dest + Src

|

| 2000 | POD | Odejmij: Dest ← Dest - Src

|

| 3000 | I | Oraz: Cel ← Cel ∧ Src

|

| 4000 | BIC | Wyczyść bit: Dest ← Dest ∧ (-1 - Src)

|

| 5000 | BIS | Zestaw bitów: Dest ← Dest ∨ Src

|

| 6000 | XOR | Wyłącznie lub: Dest ← Dest ⊻ Src

|

| 9000 | CMP | Porównaj: Set-flags(Src − Dest)

|

| A000 | FRAGMENT | Test bitów: Ustaw flagi (Dest ∧ Src)

|

| B000 | MOV | Przenieś: Cel ← Src

|

| C000 | CMPB | Porównaj bajt: Set-flags(Src − Dest)

|

| D000 | MOVB | Bajt przeniesienia: Dest ← Src (znak miejsca docelowego rejestru rozciąga się na bity 8-15) |

| E000 | BISB | Bit ustawiony bajt: Dest ← Dest ∨ Src

|

Niektóre instrukcje dwuoperandowe wykorzystują tryb adresowania dla jednego operandu i rejestru dla drugiego operandu:

| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Kod operacji | Rej | źródło/docel | Rejestr | ||||||||||||

Siedem bitów wyższego rzędu określa operację, która ma zostać wykonana, sześć bitów określa tryb adresowania operandu, a trzy bity określają rejestr lub parę rejestrów. Tam, gdzie używana jest para rejestrów (zapisana poniżej jako „Reg+1:Reg”) Reg zawiera najmniejszą część operandu. Następny rejestr o wyższym numerze zawiera wyższą część operandu (lub resztę).

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 7200 | POLANKA | Załaduj efektywny adres: Reg ← ea(Dest)

|

| 7200 | JMP | Skok: PC ← ea(Dest) (jest taki sam jak LEA PC,Dest i ma ten sam kod operacji). |

| 7400 | POPIÓŁ | Przesunięcie arytmetyczne: jeśli Src < 0 to Reg ← Shift-w prawo(Reg, -Src) inaczej Reg ← Shift-w lewo(Reg, Src)

|

| 7800 | XCH | Wymiana: Reg ↔ Src

|

| 7A00 | ASHC | Łączne przesunięcie arytmetyczne (32 bity): jeśli Src < 0 to (Reg+1:Reg) ← Shift-w prawo((Reg+1:Reg), -Src) else (Reg+1:Reg) ← Shift-w lewo(( Reg+1:Reg), Src)

|

| 7C00 | MUL | Pomnóż: (Reg+1:Reg) ← Reg × Src

|

| 7E00 | DIV | Podziel: Oblicz (Reg+1:Reg) ÷ Src; Reg ← iloraz; Reg+1 ← reszta

|

Instrukcje jednoargumentowe

Dziesięć bitów wyższego rzędu określa operację, która ma zostać wykonana, przy czym bit 15 ogólnie wybiera adresowanie bajtów i słów. Pojedyncza grupa sześciu bitów określa operand, jak zdefiniowano powyżej.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Kod operacji | źródło/docel | Rejestr | |||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0BC0 | WYMAZ | Zamień bajty słowa: Dest ← (Dest × 256) ∨ (Dest ÷ 256)

|

| 8BC0 | SWAD | Zamień cyfry bajtu: Dest ← (Dest × 16) ∨ (Dest ÷ 16)

|

| 0840 | CLR | Wyczyść: Cel ← 0

|

| 8840 | CLRB | |

| 0C00 | KOM | Uzupełnienie: cel ← (-1 - cel)

|

| 8C00 | GRZEBIEŃ | |

| 0C80 | INC | Przyrost: cel ← cel + 1

|

| 8C80 | INCB | |

| 0CC0 | grudzień | Zmniejszenie: Cel ← Cel − 1

|

| 8CC0 | GRUDZIEŃ | |

| 0C40 | NEG | Negata: Cel ← -Dest

|

| 8C40 | NEGB | |

| 0B00 | USTAWIĆ | Zestaw: Cel ← -1

|

| 8B00 | SETB | |

| 0A80 | TST | Test: Ustaw flagi (Src)

|

| 8A80 | TSTB | |

| 0A00 | ROR | Obróć w prawo: Cel: Cflag ← Obróć w prawo (Dest: Cflag, 1)

|

| 8A00 | ROB | |

| 0A40 | ROL | Obróć w lewo: Cflag:Dest ← Obróć w lewo (Cflag:Dest, 1)

|

| 8A40 | ROLB | |

| 0B80 | ASR | Przesunięcie arytmetyczne w prawo: Dest ← Dest ÷ 2, znak zachowany

|

| 8B80 | ASRB | |

| 0AC0 | ASL | Przesunięcie arytmetyczne w lewo: Dest ← Dest × 2

|

| 8AC0 | ASLB | |

| 8D80 | ADC | Dodaj przeniesienie: Dest ← Dest + Cflag

|

| 8DC0 | SBC | Odejmij przeniesienie: Dest ← Dest - Cflag

|

| 0D00 | IW2 | Zwiększ słowo o 2: Cel ← Cel + 2

|

| 0DC0 | TJMP | Skok w tabeli: PC ← PC + (Dest), PC ← PC + @PC

|

| 0D80 | ZADZWOŃ | Wywołanie w tabeli: -(SP) ← PC, PC ← PC + (Dest), PC ← PC + @PC

|

| 0D40 | SXT | Przedłużenie znaku: jeśli flaga N = 1, to Cel ← -1, w przeciwnym razie Cel ← 0

|

| 8D00 | LSTS | Załaduj stan procesora: PSW ← Dest

|

| 8D40 | SSTS | Zapisz status procesora: Dest ← PSW

|

Jednoargumentowe krótkie instrukcje natychmiastowe

Siedem bitów wysokiego rzędu oraz bity 5 i 4 określają operację, która ma zostać wykonana. Pojedyncza grupa trzech bitów określa rejestr. Czterobitowe pole zliczania zawiera małą wartość bezpośrednią lub liczbę. We wszystkich przypadkach do tego pola dodawany jest jeden, tworząc zakres od 1 do 16.

| 15 | 9 | 8 | 6 | 5 | 4 | 3 | 0 | ||||||||

| Kod operacji | Rej | Op | Liczyć | ||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0800 | DODAJ | Dodaj natychmiast: Reg ← Reg + Count + 1

|

| 0810 | SUBI | Odejmij natychmiast: Reg ← Reg - Count - 1

|

| 0820 | BICI | Natychmiastowe kasowanie bitów: Reg ← Reg ∧ (-1 - (Count+1))

|

| 0830 | MOVI | Natychmiastowy ruch: Reg ← Count + 1

|

| 8800 | SSRR | Obrót w prawo wielokrotny: Reg: flaga C ← Obrót w prawo (reg: flaga C, liczba + 1)

|

| 8810 | SSLR | Wielokrotny obrót w lewo: C-flag:Reg ← Rotate-left(C-flag:Reg, Count+1)

|

| 8820 | SSRA | Prawe przesunięcie arytmetyczne wielokrotne: Reg:C-flag ← Arithmetic-shift-right(Reg, Count+1)

|

| 8830 | SSLA | Wielokrotność przesunięcia arytmetycznego w lewo: C-flag:Reg ← Arithmetic-shift-left(Reg, Count+1)

|

| 8E00 | SDRR | Podwójny obrót w prawo (33 bity): Reg+1:Reg:C-flag ← Rotate-right(Reg+1:Reg:C-flag, Count+1)

|

| 8E10 | SDLR | Podwójne wielokrotne obracanie w lewo (33 bity): C-flag:Reg+1:Reg ← Rotate-left(C-flag:Reg+1:Reg, Count+1)

|

| 8E20 | SDRA | Podwójna wielokrotność arytmetycznego przesunięcia w prawo (32 bity): Reg:Reg+1:C-flag ← Arithmetic-shift-right(Reg:Reg+1, Count+1)

|

| 8E30 | SDLA | Podwójna wielokrotność arytmetycznego przesunięcia w lewo (32 bity): C-flag:Reg:Reg+1 ← Arithmetic-shift-left(Reg:Reg+1, Count+1)

|

Instrukcje zmiennoprzecinkowe

Osiem bitów wysokiego rzędu określa operację, która ma zostać wykonana. Dwie grupy po cztery bity określają tryb adresowania źródłowego i docelowego oraz rejestr. Jeżeli pole I = 0, to wyznaczony rejestr zawiera adres argumentu, odpowiednik trybu adresowania (Rn). Jeżeli pole I = 1, wyznaczony rejestr zawiera adres adresu argumentu, odpowiednik trybu adresowania @0(Rn).

| 15 | 8 | 7 | 6 | 4 | 3 | 2 | 0 | ||||||||

| Kod operacji | I | SReg | I | DReg | |||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| F000 | FADD | Dodawanie pływające: Dest ← Dest + Src

|

| F100 | FSUB | Odejmowanie zmiennoprzecinkowe: Cel ← Cel - Src

|

| F200 | FMUL | Mnożenie zmiennoprzecinkowe: Dest ← Dest × Src

|

| F300 | FDIV | Dzielenie zmiennoprzecinkowe: Dest ← Dest ÷ Src

|

| F400 | FCMP | Pływające porównanie: Dest - Src

|

Zablokuj instrukcje transferu

Dziesięć bitów wysokiego rzędu określa operację, która ma zostać wykonana. Dwie grupy po trzy bity określają rejestry źródłowy i docelowy. We wszystkich przypadkach rejestr źródłowy zawiera adres pierwszego słowa lub bajtu pamięci, który ma zostać przeniesiony, a rejestr docelowy zawiera adres pierwszego słowa lub bajtu pamięci, który ma otrzymać przenoszone dane. Liczba przenoszonych słów lub bajtów jest zawarta w R0 jako liczba całkowita bez znaku. Liczba mieści się w zakresie od 1 do 65536. Instrukcje te są w pełni przerywalne.

| 15 | 6 | 5 | 3 | 2 | 0 | ||||||||||

| Kod operacji | SReg | DReg | |||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0E00 | MBWU | Przenieś blok słów w górę: (DReg) ← (SReg), SReg ← SReg + 2, DReg ← DReg + 2, R0 ← R0 - 1, aż R0 = 0

|

| 0E40 | MBWD | Przenieś blok słów w dół: (DReg) ← (SReg), SReg ← SReg - 2, DReg ← DReg - 2, R0 ← R0 - 1, aż R0 = 0

|

| 0E80 | MBBU | Przenieś blok bajtów w górę: (DReg) ← (SReg), SReg ← SReg + 1, DReg ← DReg + 1, R0 ← R0 - 1, aż R0 = 0

|

| 0EC0 | MBBD | Przenieś blok bajtów w dół: (DReg) ← (SReg), SReg ← SReg - 1, DReg ← DReg - 1, R0 ← R0 - 1, aż R0 = 0

|

| 0F00 | MBWA | Przenieś blok słów na adres: (DReg) ← (SReg), SReg ← SReg + 2, R0 ← R0 - 1, aż R0 = 0

|

| 0F40 | MBBA | Przenieś blok bajtów na adres: (DReg) ← (SReg), SReg ← SReg + 1, R0 ← R0 - 1, aż R0 = 0

|

| 0F80 | MABW | Przenieś adres do bloku słów: (DReg) ← (SReg), DReg ← DReg + 2, R0 ← R0 - 1, aż R0 = 0

|

| 0FC0 | MABB | Przenieś adres do bloku bajtów: (DReg) ← (SReg), DReg ← DReg + 1, R0 ← R0 - 1, aż R0 = 0

|

Instrukcje oddziałów

Starszy bajt instrukcji określa operację. Bajt niższego rzędu jest przesunięciem słowa ze znakiem względem bieżącej lokalizacji licznika programu. Pozwala to na rozgałęzienia do przodu i do tyłu w kodzie. Maksymalny zakres gałęzi to +128, -127 słów z kodu operacyjnego gałęzi.

W większości instrukcji rozgałęzienia to, czy rozgałęzienie jest zajęte, opiera się na stanie kodów warunków. Instrukcja rozgałęzienia jest zwykle poprzedzona dwuargumentową instrukcją CMP (porównanie) lub BIT (test bitowy) lub jednoargumentową instrukcją TST (test). Instrukcje arytmetyczne i logiczne również ustawiają kody warunków. W przeciwieństwie do Intela w architekturze x86 , instrukcje MOV również je ustawiają, więc instrukcja rozgałęzienia może być użyta do rozgałęzienia w zależności od tego, czy przeniesiona wartość była zerowa, czy ujemna.

| 15 | 8 | 7 | 0 | ||||||||||||

| Kod operacji | Zrównoważyć | ||||||||||||||

| Kod operacji | Mnemoniczny | Warunek lub działanie |

|---|---|---|

| 0100 | BR | Rozgałęzienie zawsze PC ← PC + (2 × rozszerzenie znaku (przesunięcie))

|

| 0200 | BNE | Gałąź, jeśli nie jest równa Z = 0

|

| 0300 | BEQ | Rozgałęzienie, jeśli równe Z = 1

|

| 0400 | BGE | Rozgałęzienie, jeśli jest większe lub równe (N ⊻ V) = 0

|

| 0500 | BLT | Rozgałęzienie, jeśli mniej niż (N ⊻ V) = 1

|

| 0600 | BGT | Gałąź, jeśli jest większa niż (Z ∨ (N ⊻ V)) = 0

|

| 0700 | BLE | Rozgałęzienie, jeśli jest mniejsze lub równe (Z ∨ (N ⊻ V)) = 1

|

| 8000 | BPL | Rozgałęzienie, jeśli plus N = 0

|

| 8100 | BMI | Rozgałęzienie, jeśli minus N = 1

|

| 8200 | BHI | Gałąź, jeśli wyższa (C ∨ Z) = 0

|

| 8300 | BLOS | Gałąź, jeśli jest niższa lub taka sama (C ∨ Z) = 1

|

| 8400 | BVC | Rozgałęzienie, jeśli przelew jest czysty V = 0

|

| 8500 | BVS | Rozgałęzienie, jeśli zestaw przelewowy V = 1

|

| 8600 | BCC lub BHIS | Rozgałęzienie, jeśli jest jasne, lub Rozgałęzienie, jeśli wyższe lub takie samo C = 0

|

| 8700 | BCS lub BLO | Rozgałęzienie, jeśli zestaw przenoszenia, lub Rozgałęzienie, jeśli niższy C = 1

|

Ograniczony zakres instrukcji rozgałęzień oznaczał, że wraz ze wzrostem kodu docelowe adresy niektórych rozgałęzień mogą stać się nieosiągalne. Programista zamieniłby jednowyrazową instrukcję Bcc na dwuwyrazową instrukcję JMP. Ponieważ JMP nie ma form warunkowych, programista zmieniłby Bcc na przeciwne znaczenie, aby rozgałęzić się wokół JMP.

SOB (Subtract One and Branch) to kolejna warunkowa instrukcja rozgałęzienia. Określony rejestr jest zmniejszany o 1, a jeśli wynik nie jest równy zeru, wykonywana jest gałąź odwrotna na podstawie 6-bitowego przesunięcia słowa.

| 15 | 9 | 8 | 6 | 5 | 0 | ||||||||||

| Kod operacji | Rej | Zrównoważyć | |||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 7600 | SZLOCH |

Odejmij jeden i rozgałęzienie: Reg ← Reg - 1; jeśli Reg ≠ 0 to PC ← PC - (2 × przesunięcie)

|

Instrukcje podprogramu

Instrukcja JSR może zapisać dowolny rejestr na stosie. Programy, które nie potrzebują tej funkcji, określają PC jako rejestr (JSR PC, adres), a podprogram zwraca się za pomocą RTN PC. Gdyby procedura została wywołana z, na przykład, „JSR R4, adres”, wówczas stara wartość R4 zostałaby zapisana na szczycie stosu, a adres powrotu (zaraz po JSR) znalazłby się w R4. Pozwala to procedurze uzyskać dostęp do wartości zakodowanych w wierszu przez podanie (R4)+ lub do wskaźników w wierszu przez podanie @(R4)+. Autoinkrementacja przesuwa się poza te dane do punktu, w którym kod wywołującego zostaje wznowiony. Taka procedura musiałaby określić RTN R4, aby powrócić do swojego wywołującego.

Formularz JSR PC,@(SP)+ może być użyty do zaimplementowania współprogramów . Początkowo adres wejściowy współprogramu jest umieszczany na stosie i od tego momentu instrukcja JSR PC,@(SP)+ jest używana zarówno dla instrukcji call, jak i return. Wynikiem tej instrukcji JSR jest wymiana zawartości komputera PC i górnego elementu stosu, a więc umożliwienie dwóm procedurom zamiany sterowania i wznowienia operacji, w przypadku gdy każda z nich została zakończona przez poprzednią zamianę.

| 15 | 9 | 8 | 6 | 5 | 3 | 2 | 0 | ||||||||

| Kod operacji | Rej | Src | Rejestr | ||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 7000 | JSR | Skok do podprogramu: -(SP) ← Reg; Rej. ← PC; PC ← Src

|

| 15 | 3 | 2 | 0 | ||||||||||||

| Kod operacji | Rej | ||||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0018 | RTN | Powrót z podprogramu: PC ← Reg; Rej ← (SP)+

|

| 0028 | PRTN | Pop stos i powrót: SP ← SP + (2 × @SP), PC ← Reg; Rej ← (SP)+

|

Instrukcje dotyczące jednego rejestru

Instrukcje te mają 13-bitowy kod operacji i trzybitowy argument w rejestrze.

| 15 | 3 | 2 | 0 | ||||||||||||

| Kod operacji | Rej | ||||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0010 | IAK | Potwierdzenie przerwania: Kod stanu potwierdzenia przerwania, Reg ← Odczyt magistrali

|

| 0020 | MSKO | Mask out: (002E) ← Reg, Mask out kod stanu

|

Implikowane instrukcje dotyczące parametrów

| 15 | 0 | ||||||||||||||

| Kod operacji | |||||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0000 | NIE | Brak operacji: nic nie rób

|

| 0001 | RESETOWANIE | Reset: Prześlij impuls resetowania do urządzeń I/O

|

| 0002 | IEN | Zezwolenie na przerwanie: I2 ← 1

|

| 0003 | IDS | Blokada przerwań: I2 ← 0

|

| 0004 | POSTÓJ | Zatrzymaj: Wykonuje wybraną opcję zatrzymania

|

| 0005 | XCT | Wykonaj pojedynczą instrukcję: PC ← (SP)+, PS ← (SP)+, ustaw flagę śledzenia, wykonaj kod operacji, -(SP) ← PS, -(SP) ← PC, zeruj flagę śledzenia, jeśli nie ma błędu PC ← (0020 ) inny PC ← (001E)

|

| 0006 | BPT | Pułapka punktu przerwania: -(SP) ← PS, -(SP) ← PC, PC ← (002C)

|

| 0007 | WFI | Czekaj na przerwanie: Włącz przerwania (I2 ← 1). Ustaje działalność autobusowa.

|

| 0008 | RSVC | Powrót z wezwania przełożonego (B lub C): REST, SP ← SP + 2, RTT

|

| 0009 | RRTT | Powrót i powrót z pułapki: REST, RTT

|

| 000A | RATOWAĆ | Zapisz rejestry: -(SP) ← R5, -(SP) ← R4, -(SP) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0

|

| 000B | SAVS | Stan zapisu: ZAPISZ, -(SP) ← (002E), (002E) ← (002E) ∨ Maska, MSKO, IEN. Uwaga Maska jest zapisywana w drugim słowie instrukcji.

|

| 000C | ODPOCZYNEK | Przywróć rejestry: R0 ← (SP)+, R1 ← (SP)+, R2 ← (SP)+, R3 ← (SP)+, R4 ← (SP)+, R5 ← (SP)+

|

| 000D | RRTN | Przywróć i wróć: ODPOCZYNEK, PC ← (SP)+

|

| 000E | RSTS | Stan przywracania: (002E) ← (SP)+, MSKO, REST, RTT

|

| 000F | RTT | Powrót z pułapki: PC ← (SP)+, PS ← (SP)+

|

Dzwoni przełożony

Instrukcje te służą do implementacji wywołań systemu operacyjnego (nadzorcy). Wszystkie mają sześciobitowy argument rejestru. SVCB i SVCC zostały zaprojektowane w taki sposób, aby argumenty kierowane do systemu operacyjnego mogły wykorzystywać większość trybów adresowania obsługiwanych przez natywny zestaw instrukcji.

| 15 | 6 | 5 | 0 | ||||||||||||

| Kod operacji | arg | ||||||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0040 | SVCA | Wywołanie przełożonego A: -(SP) ← PS ,-(SP) ← PC, PC ← (0022) + Arg × 2, PC ← (PC)

|

| 0080 | SVCB | Wywołanie przełożonego B: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP ) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0024)

|

| 00C0 | SVCB | Wywołanie przełożonego C: TMPA ← SP, -(SP) ← PS, -(SP) ← PC, TMPB ← SP, -(SP) ← TMPA, -(SP) ← R5, -(SP) ← R4, -(SP ) ← R3, -(SP) ← R2, -(SP) ← R1, -(SP) ← R0, R1 ← TMPB, R5 ← Arg × 2, PC ← (0026)

|

Operacje na kodzie warunku

| 15 | 4 | 3 | 2 | 1 | 0 | ||||||||||

| Kod operacji | N | Z | V | C | |||||||||||

| Kod operacji | Mnemoniczny | Operacja |

|---|---|---|

| 0030 | przewoźnik niskokosztowy | Kody stanu obciążenia: Załaduj zgodnie z bitami N, Z, V, C

|

Cztery kody stanu w słowie stanu procesora (PSW) to

- N wskazuje wartość ujemną

- Z oznacza stan zerowy (równy).

- V wskazujące stan przepełnienia , oraz

- C wskazujące na stan przenoszenia .

Zarezerwowane lokalizacje o małej ilości pamięci

Lokacje pamięci pomiędzy 0000 a 003F mają stałe funkcje zdefiniowane przez procesor. Wszystkie poniższe adresy są adresami słownymi.

| Wektor | Stan |

|---|---|

| 0000-0010 | R0 - R5, SP, PC i PS dla opcji włączania/zatrzymywania |

| 0012 | błąd magistrali PC |

| 0014 | niewektorowe przerwanie awarii zasilania PC |

| 0016 | włącz/zatrzymaj opcję przywracania zasilania komputera |

| 0018 | Błąd parzystości PC |

| 001A | zarezerwowany kod operacji PC |

| 001C | nielegalny format kodu operacji PC |

| 001E | Błąd XCT na komputerze |

| 0020 | Komputer śledzenia XCT |

| 0022 | Adres tabeli SVCA |

| 0024 | Komputer SVCB |

| 0026 | Komputer SVCC |

| 0028 | adres tablicy przerwań wektorowych (I0). |

| 002A | przerwanie niewektorowe (I1) PC |

| 002C | Komputer BPT |

| 002E | Maska przerwania priorytetu we/wy |

| 0030-003C | Notatnik zmiennoprzecinkowy |

| 003E | Błąd zmiennoprzecinkowy PC |

Wydajność

Szybkość procesora WD16 różni się w zależności od szybkości zegara, konfiguracji pamięci, kodu operacji i trybów adresowania. Taktowanie instrukcji składa się z maksymalnie trzech elementów: wykonania/pobrania samej instrukcji oraz czasu dostępu do źródła i miejsca docelowego. Ostatnie dwa składniki zależą od trybu adresowania. Na przykład przy 3,3 MHz instrukcja w postaci ADD x (Rm ) , y (Rn ) ma czas pobrania/wykonania wynoszący 3,6 mikrosekundy plus czas źródłowy równy 3 mikrosekundy i czas docelowy równy 3,3 mikrosekundy, co daje całkowitą instrukcję czas 10 mikrosekund. Rejestr do rejestru ADD Rm , R n wykonuje się w 3,6 mikrosekundy. Zmiennoprzecinkowy jest znacznie wolniejszy. Instrukcja dodawania zmiennoprzecinkowego o precyzji półtorej (48 bitów) mieści się w zakresie od 60 do 140 mikrosekund. Precyzja WD16 to kompromis pomiędzy tradycyjnymi spławikami o pojedynczej i podwójnej precyzji.

Dla kontrastu, najszybszym komputerem PDP-11 w tamtym czasie był PDP-11/70. Rozkaz w postaci ADD x (Rm ) , y (Rn ) ma czas pobrania/wykonania równy 1,35 mikrosekundy plus czasy źródła i celu po 0,6 mikrosekundy, co daje całkowity czas rozkazu równy 2,55 mikrosekundy. Każdy przypadek, w którym adresowana pamięć nie znajdowała się w pamięci podręcznej, dodaje 1,02 mikrosekundy. Rejestr do rejestru ADD Rm , Rn można wykonać z pamięci podręcznej w ciągu 0,3 mikrosekundy. Zmiennoprzecinkowa instrukcja dodawania o pojedynczej precyzji wykonywana przez koprocesor FP11-C może wynosić od 0,9 do 2,5 mikrosekundy plus czas na pobranie operandów, który może wynosić do 4,2 mikrosekundy.

Instrukcje transferu bloków WD16 w przybliżeniu podwajają prędkość ruchów i blokują wejścia/wyjścia. Słowo przeniesione za pomocą instrukcji MOV (R1)+,(R2)+, SOB R0,loop zajmuje 10,6 mikrosekundy na iterację. Odpowiednik MBWU R1, R2 zajmuje 5,3 mikrosekundy na iterację.

Stowarzyszenie Użytkowników Komputerów przeprowadziło serię testów porównawczych systemu opartego na AM-100T, który kosztował 35 680 USD (równowartość 117 343 USD w 2021 r.). Okazało się, że ich test porównawczy związany z procesorem został wykonany w 31,4 sekundy na AM-100T w porównaniu do 218 sekund w przypadku przeciętnego systemu dla jednego użytkownika w przedziale cenowym od 15 000 do 25 000 USD. W grupie komputerów dla wielu użytkowników w cenie od 25 000 do 50 000 USD AM-100T znajdował się w „górnej trzeciej” szybkości.

Creative Computing Benchmark z maja 1984 roku umieścił WD16 (w aplikacji AM-100T) na 34 miejscu ze 183 testowanych maszyn. Upływający czas wyniósł 10 sekund, w porównaniu do 24 sekund dla IBM PC .

Emulator

Virtual Alpha Micro to emulator WD16 o otwartym kodzie źródłowym. Napisany w C, emuluje procesor WD16 i środowisko sprzętowe Alpha Micro AM-100. Autor twierdzi, że działa na komputerach z systemami Linux (w tym Raspberry Pi), Windows i Macintosh, chociaż nie ma żadnych plików binarnych. Będzie obsługiwać system operacyjny Alpha Micro (AMOS) i wszystkie powiązane programy. W 2002 roku firma Alpha Micro udzieliła ograniczonego pozwolenia na dystrybucję plików binarnych AMOS 4.x lub 5.0, w tym instrukcji, wyłącznie do użytku hobbystycznego.