Wymiana lampy błyskowej NOR

Chociaż pamięć flash pozostaje jedną z najpopularniejszych pamięci w systemach wbudowanych ze względu na jej nieulotność , odporność na wstrząsy, niewielkie rozmiary i niskie zużycie energii, jej zastosowanie znacznie wykroczyło poza pierwotny projekt. Opierając się na swojej oryginalnej konstrukcji, pamięć flash NOR jest przeznaczona do przechowywania binarnego kodu programów, ponieważ obsługuje XIP (eXecute-In-Place) i wysoką wydajność w operacjach odczytu, podczas gdy pamięć NAND flash jest używana do przechowywania danych ze względu na niższą cenę i wyższą wydajność operacji zapisu/kasowania w porównaniu z pamięcią NOR flash. W ostatnich latach cena pamięci flash NAND spadała znacznie szybciej niż pamięć flash NOR. Tak więc, aby ostatecznie obniżyć koszty sprzętu, użycie pamięci flash NAND w celu zastąpienia pamięci flash NOR (motywowane silnym popytem na rynku) staje się nowym trendem w projektach systemów wbudowanych, zwłaszcza w telefonach komórkowych i grach zręcznościowych .

Przegląd

Wymiana zależy od dobrze zaprojektowanego zarządzania pamięcią flash, które jest realizowane przez oprogramowanie w systemie hosta (jako surowy nośnik) lub obwody sprzętowe/oprogramowanie układowe wewnątrz jego urządzeń. W tym miejscu zaproponowano wydajny mechanizm przewidywania z ograniczonymi wymaganiami dotyczącymi pamięci i wydajną implementację. Mechanizm predykcji zbiera wzorce dostępu do wykonania programu w celu skonstruowania grafu predykcji poprzez przyjęcie zbioru roboczego . Zgodnie z wykresem przewidywania, mechanizm przewidywania wstępnie pobiera dane (/kod) do SRAM pamięci podręcznej, aby zmniejszyć wskaźnik chybień w pamięci podręcznej. W związku z tym poprawia się wydajność wykonywania programu, a luka w wydajności odczytu między NAND i NOR jest skutecznie wypełniana. Używanie NAND Flash do kodu rozruchowego wymaga użycia pamięci DRAM do cieniowania kodu.

Skuteczna strategia pobierania wstępnego

W odróżnieniu od popularnych koncepcji buforowania w hierarchii pamięci , podejście to ma na celu zorientowany na aplikację mechanizm buforowania, który przyjmuje wstępne pobieranie wspomagane przewidywaniem na podstawie określonych śladów wykonania aplikacji. Projekty systemów wbudowanych rozpatrywane są z ograniczonym zestawem aplikacji, takim jak zestaw wybranych programów systemowych w telefonach komórkowych czy gry zręcznościowe automatów do parków rozrywki. Poza tym pojemność SRAM i moc obliczeniowa są ograniczone podczas implementacji.

Architektura sprzętowa

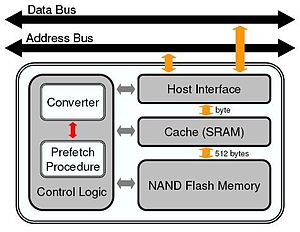

Projekt sprzętu obejmuje cztery podstawowe komponenty: interfejs hosta, SRAM (pamięć podręczna), pamięć flash NAND i logikę sterowania. Aby wypełnić lukę w wydajności między NAND i NOR, SRAM służy jako warstwa pamięci podręcznej dla dostępu do danych przez NAND. Interfejs hosta odpowiada za komunikację z systemem hosta poprzez magistrale adresowe i danych . Co najważniejsze, logika kontrolna zarządza buforowaniem i zapewnia emulację usługi NOR flash z NAND flash i SRAM; musi mieć zaimplementowany inteligentny mechanizm przewidywania w celu poprawy wydajności systemu. Logika sterowania składa się z dwóch głównych elementów: Konwerter emuluje dostęp do pamięci flash NOR za pośrednictwem pamięci flash NAND z pamięcią podręczną SRAM, w której translacja adresu musi odbywać się z adresowania bajtowego (dla NOR) na adres bloku logicznego (LBA) adresowanie (dla NAND). Należy zauważyć, że każda strona 512B/2KB NAND odpowiada odpowiednio jednemu i czterem LBA. Procedura pobierania wstępnego próbuje pobierać dane z pamięci NAND do pamięci SRAM tak, aby współczynnik trafień dostępu NOR był wysoki w porównaniu z pamięcią SRAM. Procedura powinna przeanalizować i wyodrębnić zachowanie aplikacji docelowej za pomocą zestawu zebranych śladów. Zgodnie z wydobytymi wzorcami dostępu z zebranych śladów, procedura generuje informacje predykcyjne, określane jako graf predykcyjny.

Wykres prognozy

Wzorzec dostępu wykonywania aplikacji przez NOR (lub NAND) składa się z sekwencji LBA. Ponieważ aplikacja jest uruchamiana wiele razy, może pojawić się „praktycznie” pełny obraz możliwego wzorca dostępu do wykonania aplikacji. Ponieważ większość wykonań aplikacji jest zależna od danych wejściowych lub sterowana danymi, po danym LBA może występować więcej niż jeden kolejny LBA, gdzie każdy LBA odpowiada jednemu węzłowi na grafie. Węzły z więcej niż jednym kolejnym LBA nazywane są węzłami rozgałęzionymi, a pozostałe nazywane są węzłami zwykłymi. Wykres, który odpowiada wzorcom dostępu, jest określany jako wykres przewidywania określonej aplikacji. Jeśli strony w pamięci NAND flash mogłyby być wstępnie pobierane na czas, a w pamięci SRAM jest wystarczająca ilość miejsca na buforowanie, wówczas wszystkie dostępy do danych mogłyby odbywać się za pośrednictwem pamięci SRAM.

Aby zapisać wykres predykcji w pamięci flash przy zminimalizowanych narzutach (pojemność SRAM), kolejne informacje LBA każdego zwykłego węzła są zapisywane w wolnym obszarze odpowiedniej strony. Dzieje się tak dlatego, że w obecnych implementacjach wolny obszar strony jest niewykorzystany, a odczytanie strony zwykle wiąże się z jednoczesnym odczytem jej danych i wolnych obszarów. W ten sposób dostęp do kolejnych informacji LBA zwykłego węzła odbywa się bez dodatkowych kosztów. Ponieważ węzeł oddziału ma więcej niż jeden kolejny adres LBA, w wolnym obszarze odpowiedniej strony może nie być wystarczającej ilości wolnego miejsca do przechowywania informacji. W ten sposób utrzymywana jest tablica rozgałęzień w celu zapisania kolejnych informacji LBA wszystkich węzłów rozgałęzień. Początkowy adres wpisu tabeli rozgałęzień, który odpowiada węzłowi rozgałęzienia, można zapisać w wolnym obszarze odpowiedniej strony. Wpis początkowy rejestruje liczbę kolejnych LBA węzła rozgałęzienia, a kolejne LBA są przechowywane we wpisach następujących po wpisie początkowym. Tabela oddziałów może być zapisana w pamięci flash. Podczas run time , cała tabela może zostać załadowana do SRAM w celu uzyskania lepszej wydajności. Jeśli nie ma wystarczającej ilości miejsca w SRAM, części tabeli można załadować na żądanie .

Procedura pobierania wstępnego

Celem procedury pobierania wstępnego jest wstępne pobieranie danych z pamięci NAND na podstawie danego wykresu predykcji, tak aby większość dostępów do danych odbywała się w pamięci SRAM. Podstawową ideą jest wstępne pobieranie danych zgodnie z kolejnością LBA na grafie. W celu sprawnego wyszukania wybranej strony w pamięci podręcznej w zarządzaniu pamięcią podręczną przyjęto cykliczną kolejkę . Z drugiej strony dane pobrane z pamięci flash NAND są umieszczane w kolejce, podczas gdy dane przesyłane do hosta są usuwane z kolejki. Procedura pobierania z wyprzedzeniem jest wykonywana w trybie zachłannym sposób: Niech P1 będzie ostatnią wstępnie pobraną stroną. Jeśli P1 odpowiada zwykłemu węzłowi, to strona odpowiadająca kolejnemu LBA jest pobierana z wyprzedzeniem. Jeśli P1 odpowiada węzłowi rozgałęzienia, wówczas procedura powinna pobierać strony z wyprzedzeniem, podążając za wszystkimi możliwymi następnymi łączami LBA w równej bazie iw sposób okrężny .

Wymiana 2D NAND na 3D NAND

Od 2021 r. Rozpoczęła się wymiana 2D NAND na 3D NAND. Zaletą 3D NAND jest niższy koszt na bit i najnowsza technologia kontrolera zapewniająca większą niezawodność. W rezultacie, nawet przy niskim poziomie GB, 3D NAND jest preferowaną opcją przechowywania kodu.