Zasady włączania pamięci podręcznej

Wielopoziomowe pamięci podręczne można projektować na różne sposoby w zależności od tego, czy zawartość jednej pamięci podręcznej jest obecna w innych poziomach pamięci podręcznych. Jeśli wszystkie bloki w pamięci podręcznej wyższego poziomu są również obecne w pamięci podręcznej niższego poziomu, wówczas mówi się, że pamięć podręczna niższego poziomu obejmuje pamięć podręczną wyższego poziomu. Jeśli pamięć podręczna niższego poziomu zawiera tylko bloki, których nie ma w pamięci podręcznej wyższego poziomu, wówczas mówi się, że pamięć podręczna niższego poziomu wyklucza pamięć podręczną wyższego poziomu. Jeśli zawartość pamięci podręcznej niższego poziomu nie obejmuje ani nie wyklucza pamięci podręcznej wyższego poziomu, nazywa się to pamięcią podręczną niewyłączną niewyłączną (DZIEWIĘĆ) .

Polityka integracyjna

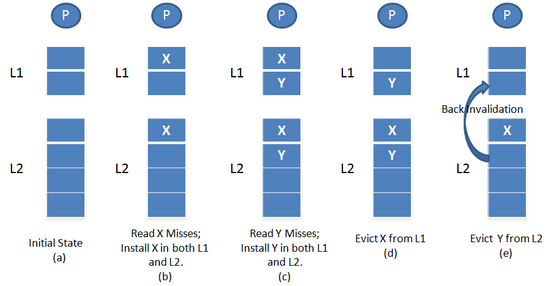

Rozważmy przykład dwupoziomowej hierarchii pamięci podręcznej , w której L2 może być włączająca, wykluczająca lub DZIEWIĘĆ z L1. Rozważmy przypadek, gdy L2 zawiera L1. Załóżmy, że procesor żąda odczytu bloku X. Jeśli blok zostanie znaleziony w pamięci podręcznej L1, wówczas dane są odczytywane z pamięci podręcznej L1 i zwracane do procesora. Jeżeli blok nie zostanie znaleziony w pamięci podręcznej L1, ale jest obecny w pamięci podręcznej L2, wówczas blok pamięci podręcznej jest pobierany z pamięci podręcznej L2 i umieszczany w pamięci podręcznej L1. Jeśli spowoduje to usunięcie bloku z L1, nie ma udziału L2. Jeśli blok nie zostanie znaleziony ani w L1, ani w L2, to jest pobierany z pamięci głównej i umieszczany zarówno w L1, jak i L2. Teraz, jeśli nastąpi eksmisja z L2, pamięć podręczna L2 wysyła wsteczne unieważnienie do pamięci podręcznej L1, aby włączenie nie zostało naruszone.

Jak pokazano na rysunku 1, początkowo załóżmy, że obie pamięci podręczne L1 i L2 są puste (a). Załóżmy, że procesor wysyła żądanie odczytu X. Będzie to chybienie zarówno w L1, jak i L2, a zatem blok jest przenoszony zarówno do L1, jak i L2 z pamięci głównej , jak pokazano na (b). Załóżmy teraz, że procesor wysyła żądanie odczytu Y, które jest chybione zarówno w L1, jak i L2. Tak więc blok Y jest umieszczony zarówno w L1, jak i L2, jak pokazano na (c). Jeśli blok X musi zostać eksmitowany z L1, to jest usuwany z L1 tylko tak, jak pokazano w (d). Jeśli blok Y musi zostać eksmitowany z L2, wysyła żądanie unieważnienia wstecznego do L1, a zatem blok Y jest eksmitowany z L1, jak pokazano w (e).

Aby inkluzja się utrzymała, muszą być spełnione pewne warunki. Asocjatywność L2 musi być większa lub równa asocjatywności L1, niezależnie od liczby zestawów. Liczba zestawów L2 musi być większa lub równa liczbie zestawów L1, niezależnie od asocjatywności L2. Wszystkie informacje referencyjne z warstwy L1 są przekazywane do warstwy L2, aby mogła ona zaktualizować swoje zastępcze .

Jednym z przykładów zintegrowanej pamięci podręcznej jest czterordzeniowy procesor Intel z 4x256 KB pamięci podręcznej L2 i 8 MB (włącznie) pamięci podręcznej L3.

Ekskluzywna polityka

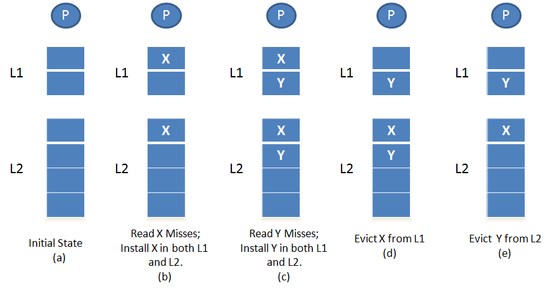

Rozważmy przypadek, gdy L2 wyklucza L1. Załóżmy, że procesor żąda odczytu bloku X. Jeśli blok zostanie znaleziony w pamięci podręcznej L1, wówczas dane są odczytywane z pamięci podręcznej L1 i zwracane do procesora. Jeśli blok nie zostanie znaleziony w pamięci podręcznej L1, ale jest obecny w pamięci podręcznej L2, wówczas blok pamięci podręcznej jest przenoszony z pamięci podręcznej L2 do pamięci podręcznej L1. Jeśli spowoduje to eksmisję bloku z L1, eksmitowany blok jest następnie umieszczany w L2. Tylko w ten sposób zapełnia się L2. Tutaj L2 zachowuje się jak pamięć podręczna ofiary . Jeśli blok nie zostanie znaleziony ani w L1, ani w L2, to jest pobierany z pamięci głównej i umieszczany tylko w L1, a nie w L2.

Jak pokazano na rysunku 2, początkowo załóżmy, że obie pamięci podręczne L1 i L2 są puste (a). Załóżmy, że procesor wysyła żądanie odczytu X. Będzie to chybienie zarówno w L1, jak i L2, a zatem blok jest przenoszony do L1 z pamięci głównej, jak pokazano w (b). Teraz ponownie procesor wysyła żądanie odczytu Y, które jest chybione zarówno w L1, jak i L2. Tak więc blok Y jest umieszczany w L1, jak pokazano na (c). Jeśli blok X musi zostać eksmitowany z L1, to jest usuwany z L1 i umieszczany w L2, jak pokazano na (d).

Przykładem ekskluzywnej pamięci podręcznej jest AMD Opteron z 512 KB (na rdzeń) pamięci podręcznej L2, z wyłączeniem L1.

Polityka NINE

Rozważmy przypadek, gdy L2 jest niewyłączny niewyłączny L1. Załóżmy, że procesor żąda odczytu bloku X. Jeśli blok znajduje się w pamięci podręcznej L1, dane są odczytywane z pamięci podręcznej L1 i zwracane do procesora. Jeżeli blok nie zostanie znaleziony w pamięci podręcznej L1, ale jest obecny w pamięci podręcznej L2, wówczas blok pamięci podręcznej jest pobierany z pamięci podręcznej L2 i umieszczany w pamięci podręcznej L1. Jeśli spowoduje to eksmisję bloku z L1, nie ma udziału L2, czyli tak samo jak w przypadku polityki inkluzyjnej. Jeśli blok nie zostanie znaleziony zarówno w L1, jak i L2, to jest pobierany z pamięci głównej i umieszczany zarówno w L1, jak i L2. Teraz, jeśli jest eksmisja z L2, w przeciwieństwie do polityki włączającej, nie ma wstecznego unieważnienia.

Jak pokazano na rysunku 3, początkowo załóżmy, że obie pamięci podręczne L1 i L2 są puste (a). Załóżmy, że procesor wysyła żądanie odczytu X. Będzie to chybienie zarówno w L1, jak i L2, a zatem blok jest przenoszony zarówno do L1, jak i L2 z pamięci głównej, jak pokazano na (b). Teraz ponownie procesor wysyła żądanie odczytu Y, które jest chybione zarówno w L1, jak i L2. Tak więc blok Y jest umieszczony zarówno w L1, jak i L2, jak pokazano na (c). Jeśli blok X musi zostać eksmitowany z L1, to jest usuwany z L1 tylko tak, jak pokazano w (d). Jeśli blok Y musi zostać eksmitowany z L2, jest eksmitowany z L2 tylko tak, jak pokazano w (e).

Przykładem niewyłącznej niewyłącznej pamięci podręcznej jest AMD Opteron z niewyłączną pamięcią podręczną L3 o wielkości 6 MB (współużytkowana).

Porównanie

Zaleta polityki włączania polega na tym, że w systemach równoległych z prywatną pamięcią podręczną przypadającą na procesor, jeśli brakuje pamięci podręcznej, inne równorzędne pamięci podręczne są sprawdzane pod kątem blokady. Jeśli pamięć podręczna niższego poziomu obejmuje pamięć podręczną wyższego poziomu i jest to brak w pamięci podręcznej niższego poziomu, wówczas nie trzeba przeszukiwać pamięci podręcznej wyższego poziomu. Oznacza to krótsze opóźnienie chybienia dla pamięci podręcznej włącznie w porównaniu z ekskluzywnymi i NINE.

Wadą polityki włączania jest to, że unikalna pojemność pamięci podręcznej jest określana przez pamięć podręczną niższego poziomu. Inaczej niż w przypadku wyłącznej pamięci podręcznej, gdzie unikalna pojemność pamięci jest sumą pojemności wszystkich pamięci podręcznych w hierarchii. Jeśli rozmiar pamięci podręcznej niższego poziomu jest mały i porównywalny z rozmiarem pamięci podręcznej wyższego poziomu, jest więcej zmarnowanej pojemności pamięci podręcznej w pamięciach podręcznych obejmujących. Chociaż ekskluzywna pamięć podręczna ma większą unikalną pojemność pamięci, zużywa więcej przepustowości, ponieważ cierpi z powodu wyższego wskaźnika wypełniania nowych bloków (równego wskaźnikowi chybień pamięci podręcznej wyższego poziomu) w porównaniu z pamięcią podręczną NINE, która jest wypełniana tylko nowym blokiem kiedy chybia. W związku z tym ocena kosztów w stosunku do korzyści musi być przeprowadzona przy wykorzystaniu możliwości wyboru między pamięciami podręcznymi Inclusive, Exclusive i NINE.

Włączenie wartości : nie jest konieczne, aby blok miał te same wartości danych, gdy jest buforowany zarówno w pamięciach podręcznych wyższego, jak i niższego poziomu, nawet jeśli włączenie jest zachowane. Ale jeśli wartości danych są takie same, włączenie wartości jest zachowane. Zależy to od używanej zasady zapisu, ponieważ zasada zapisu zwrotnego nie powiadamia pamięci podręcznej niższego poziomu o zmianach wprowadzonych w bloku w pamięci podręcznej wyższego poziomu. Jednak w przypadku pamięci podręcznej zapisu nie ma takiego problemu.

- ^ abc Solihin , Yan ( 2016). Podstawy równoległej architektury wielordzeniowej . Chapmana i Halla/CRC. s. 146–150. ISBN 9781482211184 .

- Bibliografia _ Gupta, Anoop; Singh, Jaswinder Pal (1999). Architektura komputerów równoległych: podejście sprzętowo-programowe . San Francisco: Wydawcy Morgan Kaufmann. s. 369 –372. ISBN 1558603433 .

- ^ a b c „Porównywanie architektur pamięci podręcznej i protokołów spójności w wielordzeniowych systemach SMP x86-64” . Materiały z 42. Międzynarodowego Sympozjum Mikroarchitektury . MIKRO'09.

- Bibliografia _ Davis, BT; Jordania, M. (2004). „Ocena wydajności wyłącznych hierarchii pamięci podręcznej”. Międzynarodowe sympozjum IEEE na temat analizy wydajności systemów i oprogramowania ISPASS, 2004 . s. 89–96. doi : 10.1109/ISPASS.2004.1291359 . ISBN 0-7803-8385-0 .