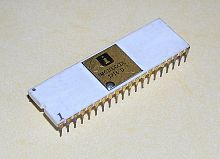

Intersil 6100

Intersil 6100 to jednoukładowa implementacja mikroprocesora 12-bitowego zestawu instrukcji PDP-8 wraz z szeregiem układów scalonych obsługujących urządzenia peryferyjne i pamięci opracowanych przez firmę Intersil w połowie lat siedemdziesiątych. Czasami nazywano go CMOS-PDP8 . Ponieważ był również produkowany przez Harris Corporation , był również znany jako Harris HM-6100 . Intersil 6100 został wprowadzony w drugim kwartale 1975 roku, a wersja Harrisa w 1976 roku.

Rodzina 6100 została wyprodukowana przy użyciu CMOS , a nie technologii bipolarnych i NMOS używanych przez większość jej współczesnych ( Z80 , 8080 , 6502 , 6800 , 9900 itd.). Dzięki technologii CMOS i niskim częstotliwościom taktowania, 8 MHz dla Harris HM-6100A, miał stosunkowo niski pobór mocy, poniżej 100 mW przy 10 V/2 MHz, i mógł być zasilany z jednego źródła w szerokim zakresie częstotliwości. zakres 4–11 V. Dzięki temu może być stosowany w systemach wbudowanych o wysokiej niezawodności bez potrzeby jakiegokolwiek znaczącego zarządzania termicznego, jeśli reszta systemu była również CMOS.

6100 był dostępny w specyfikacji wojskowej, a ponieważ był dostarczany z dwóch źródeł przez Intersil i Harris, był używany w niektórych produktach wojskowych jako alternatywa o niskim poborze mocy dla 8080, 6800 itp. Chociaż miał bardzo prosty zestaw instrukcji i architekturę, to doskonale nadawał się do stosowania w systemach wbudowanych, które wcześniej korzystały z dyskretnych obwodów logicznych, a nawet zmotoryzowanych przełączników obrotowych Ledex lub kontrolerów logicznych opartych na przekaźnikach.

Rodzina 6100 była używana w wielu produktach komercyjnych, w tym w linii DECmate , pierwszej próbie DEC wyprodukowania komputera osobistego . Według Byte , Intersil 6100 został po raz pierwszy użyty w PCM-12 Pacific Cyber / Metrix w 1976 roku. Intersil sprzedawał układy scalone do 1982 roku jako rodzina IM6100. Cena nie była konkurencyjna, a oferta nie powiodła się. IBM PC w 1981 roku scementował zagładę „CMOS-8”.

Opis

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

6100 to 12-bitowy procesor, który ściśle emuluje PDP-8 (zobacz PDP-8, aby uzyskać pełniejszą dyskusję). Ma trzy podstawowe rejestry: PC ( licznik programu ), 12-bitowy AC ( akumulator ) i MQ (iloraz mnożnika). Wszystkie instrukcje dwuargumentowe odczytują AC i MQ i zapisują z powrotem do AC.

Nie ma wskaźnika stosu; podprogramy wracają do swoich funkcji wywołujących, przeskakując z powrotem do głównego kodu, zazwyczaj przechowując adres zwrotny w pierwszym słowie samego podprogramu. Utrudnia to posiadanie podprogramów w pamięci ROM, które muszą znaleźć inną lokalizację do przechowywania adresu. Nie stanowiło to problemu dla oryginalnego PDP-8, w którym cała pamięć główna była przeznaczona do odczytu/ zapisu .

Warunkowe w 6100 pozwalają na pominięcie tylko następnej instrukcji. Gałęzie są konstruowane z warunkowym i następującym skokiem. Jest tylko jedno przerwanie maskowalne. Kiedy przerwanie jest wyzwalane, CPU zapisuje bieżący PC w 0000, a następnie rozpoczyna wykonywanie od 0001. Przerwanie może być wyłączone lub włączone przy użyciu instrukcji IOF i ION (lub SKON).

6100 ma 12-bitową magistralę danych/adresową, ograniczającą pamięć RAM do zaledwie 4K słów lub 6 KB. Odniesienia do pamięci są 7-bitowe, przesunięte albo od adresu 0, albo od adresu bazowego strony PC (uzyskanego przez ustawienie siedmiu najmniej znaczących bitów PC na zero). Pamięć można było rozszerzyć za pomocą opcjonalnego układu pomocniczego 6102, który dodał trzy linie adresowe , a tym samym rozszerzył pamięć do 32 000 słów (48 KB) w taki sam sposób, w jaki PDP-8 / E rozszerzył PDP-8. 6102 ma dwa wewnętrzne rejestry, IFR (rejestr pola instrukcji) i DFR (rejestr pola danych), które przesuwają stronę 4K, gdy procesor uzyskuje dostęp do pamięci.

Wersje i sprzęt pomocniczy

Intersil oferował różne powiązane chipy do obsługi systemów 6100. Procesor IM6100 implementuje prostą 8 (podstawowy PDP-8 bez sprzętu do mapowania pamięci). IM6101 PIE (Programmable Interface Element) to podstawowy port I/O PDP-8. IM6102 MEDIC (rozszerzenie pamięci, kontroler DMA, timer interwałowy) przekształca IM6100 w coś przypominającego procesor PDP-8/E. IM6103 PIO (równoległy port wejścia-wyjścia) oraz IM6402 lub IM6403 UART to podstawowe urządzenia we/wy PDP-8 na układach scalonych.

Intersil oferował również kompatybilne rozmiary pamięci RAM i ROM : IM6551 i IM6561 (1 Kbit, 256 × 4) SRAM , IM6512 (768 bitów, 64x12) SRAM oraz IM6312 (12 Kbit, 1024 × 12) programowalna maska PROM .

Wybór tych komponentów był oferowany jako zestaw Intersil 6801 CMOS Family Sampler Kit z 6960 - Sampler PC Board, system jednopłytowy zawierający procesor IM6100, IM6101 PIE, IM6312 ODT (Octal Debugging Technique) Monitor ROM, trzy 256 × 4 CMOS RAM i UART IM6403.

Podstawowy 6100 został później zaktualizowany do 6120 z wbudowanym kontrolerem pamięci 6102.

Linki zewnętrzne

- „Architektura mikroprocesora Intersil 6100” , CPU World

- Intersil, „IM6100 CMOS Family Sampler” zarchiwizowany 2014-10-02 w Wayback Machine