Rozszerzenie rozmiaru strony

W informatyce rozszerzenie rozmiaru strony ( PSE ) odnosi się do funkcji procesorów x86 , która umożliwia tworzenie stron większych niż tradycyjny rozmiar 4 KiB . Został on wprowadzony w oryginalnym Pentium , ale został publicznie udokumentowany przez firmę Intel dopiero wraz z wydaniem Pentium Pro . Instrukcja CPUID może być użyta do określenia dostępności PSE na procesorach x86 .

Motywacja

Wyobraź sobie następujący scenariusz. Program użytkowy żąda bloku pamięci o wielkości 1 MiB . Aby spełnić to żądanie, system operacyjny obsługujący stronicowanie i działający na starszych x86 będzie musiał przydzielić 256 stron po 4 KiB każda. Narzut 1 KiB pamięci jest wymagany do obsługi katalogów stron i tablic stron.

Podczas uzyskiwania dostępu do tej pamięci 1 MiB, każdy z 256 wpisów strony byłby buforowany w buforze translacji (TLB; pamięć podręczna, która zapamiętuje translacje adresu wirtualnego na adres fizyczny w celu szybszego wyszukiwania kolejnych żądań pamięci). Zaśmiecanie TLB jest prawdopodobnie jedną z największych wad posiadania kilku wpisów stron dla tego, co można było przydzielić w jednym bloku pamięci. Jeśli TLB zostanie zapełniony, wpis TLB musiałby zostać zwolniony, katalog stron i tablice stron musiałyby zostać „przeszukane” w pamięci, a na koniec uzyskano dostęp do pamięci i nowy wpis zostałby przeniesiony do TLB . Jest to poważny spadek wydajności i był prawdopodobnie największą motywacją do rozszerzenia architektury x86 o większe rozmiary stron.

PSE pozwala na istnienie stron o rozmiarze 4 MiB wraz ze stronami o rozmiarze 4 KiB. Opisane wcześniej żądanie 1 MiB byłoby łatwo spełnione za pomocą pojedynczej strony 4 MiB i wymagałoby tylko jednego wpisu TLB. Jednak wadą stosowania większych rozmiarów stron jest wewnętrzna fragmentacja .

Operacja

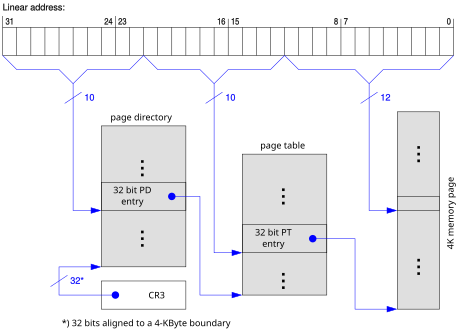

W tradycyjnym 32-bitowym trybie chronionym procesory x86 używają dwupoziomowego schematu translacji stron, w którym rejestr kontrolny CR3 wskazuje pojedynczy katalog stron o długości 4 KiB , który jest podzielony na 1024 × 4-bajtowe wpisy wskazujące na 4 KiB -długie tablice stron , podobnie składające się z 1024 × 4-bajtowych wpisów wskazujących na strony o długości 4 KiB.

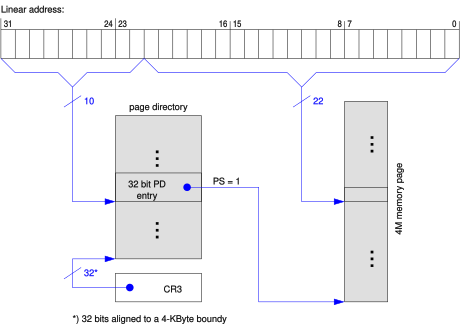

Włączenie PSE (poprzez ustawienie bitu 4, PSE , rejestru systemowego CR4 ) zmienia ten schemat. Wpisy w katalogu stron mają dodatkową flagę w bicie 7, nazwaną PS (dla rozmiaru strony ). Ta flaga została zignorowana bez PSE, ale teraz wpis katalogu strony z PS ustawionym na 1 nie wskazuje na tablicę stron, ale na pojedynczą dużą stronę 4 MiB. Wpis katalogu strony z PS ustawionym na 0 zachowuje się jak bez PSE.

w procesorze dostępna jest nowsza funkcja PSE-36 , co zostało sprawdzone za pomocą instrukcji CPUID , wówczas we wpisie katalogu strony wskazującego na dużą stronę używane są 4 dodatkowe bity oprócz normalnych 10 bitów. Pozwala to na umieszczenie dużej strony w 36-bitowej przestrzeni adresowej.

Jeśli używane jest rozszerzenie adresu fizycznego (PAE), rozmiar dużych stron jest zmniejszany z 4 MiB do 2 MiB, a PSE jest zawsze włączone, niezależnie od bitu PSE w CR4 .

Linki zewnętrzne

- Podręczniki programistów architektury Intel 64 i IA-32

- Zrozumienie 4-milionowych rozszerzeń rozmiaru strony w procesorze Pentium (Robert R. Collins)