Rozszerzenie adresu fizycznego

W informatyce rozszerzenie adresu fizycznego ( PAE ), czasami nazywane rozszerzeniem adresu strony , jest funkcją zarządzania pamięcią dla architektury x86. PAE został po raz pierwszy wprowadzony przez Intela w Pentium Pro , a później przez AMD w procesorze Athlon . Definiuje tablicy stron na trzech poziomach (zamiast dwóch), z wpisami w tablicy po 64 bity zamiast 32, umożliwiając tym procesorom bezpośredni dostęp do fizycznej przestrzeni adresowej większej niż 4 gigabajty (2 32 bajty).

Struktura tablicy stron używana przez procesory x86-64 podczas pracy w trybie długim dodatkowo rozszerza hierarchię tablicy stron do czterech poziomów, rozszerzając wirtualną przestrzeń adresową i wykorzystuje dodatkowe bity adresu fizycznego na wszystkich poziomach tablicy strony, rozszerzając fizyczną przestrzeń adresową . Wykorzystuje również najwyższy bit 64-bitowego wpisu tablicy stron jako bit no-execute lub „NX” , wskazujący, że kodu nie można wykonać z powiązanej strony. Funkcja NX jest również dostępna w trybie chronionym , gdy na tych procesorach działa 32-bitowy system operacyjny, pod warunkiem, że system operacyjny obsługuje PAE.

Historia

PAE został po raz pierwszy zaimplementowany w Intel Pentium Pro w 1995 roku, chociaż towarzyszące chipsety zwykle nie obsługiwały wymaganych dodatkowych bitów adresu.

PAE jest obsługiwane przez procesory Pentium Pro, Pentium II , Pentium III i Pentium 4 . Pierwsze Pentium M („Banias”) wprowadzone w 2003 roku również obsługują PAE; jednak nie pokazują flagi obsługi PAE w swoich CPUID . Był również dostępny na procesorach AMD, w tym AMD Athlon (chociaż chipsety są ograniczone do adresowania 32-bitowego) i późniejszych modelach procesorów AMD.

Kiedy AMD zdefiniowało swoje 64-bitowe rozszerzenie standardowej architektury x86 , AMD64 lub x86-64, udoskonaliło również system stronicowania w „ trybie długim ” opartym na PAE. Obsługuje 64-bitowe adresy wirtualne (od listopada 2018 r. Zaimplementowano 48 bitów), 52-bitowe adresy fizyczne i zawiera funkcjonalność bitową NX . Podczas inicjowania procesora x86-64 konieczne jest włączenie funkcji PAE przed przełączeniem procesora z trybu Legacy na tryb długi.

Projekt

Dzięki PAE wpis tablicy stron w architekturze x86 jest powiększany z 32 do 64 bitów. Daje to więcej miejsca na fizyczny adres strony lub pole „numer ramki strony” we wpisie tablicy stron. W początkowych implementacjach PAE pole numeru ramki strony zostało rozszerzone z 20 do 24 bitów. Rozmiar „przesunięcia bajtów” od tłumaczonego adresu nadal wynosi 12 bitów, więc całkowity rozmiar adresu fizycznego wzrasta z 32 bitów do 36 bitów (tj. z 20+12 do 24+12). Zwiększyło to pamięć fizyczną, która teoretycznie może być adresowana przez procesor z 4 GB do 64 GB.

W pierwszych procesorach, które obsługiwały PAE, obsługa większych adresów fizycznych jest widoczna w ich pinach w pakiecie, z oznaczeniami pinów adresu sięgającymi A35 zamiast zatrzymywać się na A31. Późniejsze rodziny procesorów wykorzystują połączenia międzysieciowe, takie jak Hypertransport lub QuickPath Interconnect , które nie mają dedykowanych sygnałów adresu pamięci, więc ta zależność jest mniej widoczna.

32-bitowy rozmiar adresu wirtualnego nie jest zmieniany, więc zwykłe aplikacje nadal używają instrukcji z adresami 32-bitowymi i (w modelu z płaską pamięcią ) są ograniczone do 4 gigabajtów wirtualnej przestrzeni adresowej. Systemy operacyjne obsługujące ten tryb używają tablic stron do mapowania zwykłej wirtualnej przestrzeni adresowej 4 GB na pamięć fizyczną, która w zależności od systemu operacyjnego i reszty platformy sprzętowej może mieć nawet 64 GB. Mapowanie jest zwykle stosowane osobno dla każdego procesu , więc dodatkowa pamięć RAM jest przydatna, nawet jeśli żaden pojedynczy proces nie może uzyskać do niej dostępu jednocześnie.

x86-64 przez AMD rozszerzyły teoretyczny możliwy rozmiar adresów fizycznych do 52 bitów.

Struktury tablic stron

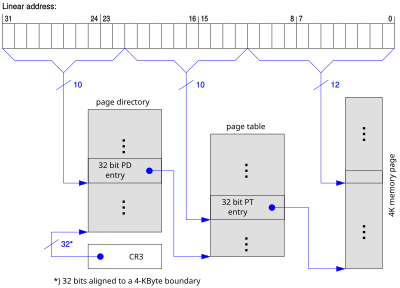

W trybie chronionym z włączonym stronicowaniem (bit 31, PG rejestru kontrolnego CR0 jest ustawiony), ale bez PAE, procesory x86 używają dwupoziomowego schematu translacji stron. Rejestr kontrolny CR3 przechowuje wyrównany do strony adres fizyczny pojedynczego katalogu strony o długości 4 KB . Jest on podzielony na 1024 czterobajtowe wpisy katalogu stron, które z kolei, jeśli są ważne, przechowują wyrównane do strony adresy fizyczne tablic stron , każdy o rozmiarze 4 KB. Te podobnie składają się z 1024 czterobajtowych wpisów tablicy stron, które, jeśli są ważne, przechowują wyrównane do strony adresy fizyczne stron o długości 4 KB pamięci fizycznej (RAM).

Włączenie PAE (poprzez ustawienie bitu 5 PAE w rejestrze systemowym CR4 ) powoduje poważne zmiany w tym schemacie. Domyślnie rozmiar każdej strony pozostaje równy 4 KB. Każdy wpis w tablicy stron i katalogu stron ma długość 64 bitów (8 bajtów) zamiast 32 bitów, aby umożliwić dodatkowe bity adresu. Jednak rozmiar każdej tabeli nie zmienia się, więc zarówno tabela, jak i katalog mają teraz tylko 512 wpisów. Ponieważ pozwala to tylko na połowę wpisów oryginalnego schematu, dodano dodatkowy poziom hierarchii, więc CR3 wskazuje teraz fizycznie na tablicę wskaźników katalogu stron , krótka tabela zawierająca cztery wskaźniki do katalogów stron.

Wpisy w katalogu stron mają dodatkową flagę w bicie 7, nazwaną PS (dla rozmiaru strony ). Jeśli system ustawił ten bit na 1 , pozycja katalogu strony nie wskazuje na tablicę stron, ale na pojedynczą, dużą stronę o wielkości 2 MB ( rozszerzenie rozmiaru strony ).

We wszystkich formatach tablic stron obsługiwanych przez x86 i x86-64 12 najmniej znaczących bitów wpisu tablicy stron jest albo interpretowanych przez jednostkę zarządzania pamięcią, albo jest zarezerwowanych do użytku przez system operacyjny. W procesorach, które implementują funkcję „brak wykonywania” lub „wyłączanie wykonywania”, najbardziej znaczący bit (bit 63) to bit NX . Kolejnych jedenaście najbardziej znaczących bitów (bity od 52 do 62) jest zarezerwowanych do użytku przez system operacyjny zarówno w specyfikacjach architektury Intela, jak i AMD. Zatem z 64 bitów we wpisie tablicy stron, 12 bitów niskiego i 12 bitów wysokiego rzędu ma inne zastosowania, pozostawiając 40 bitów (bity od 12 do 51) na fizyczny numer strony. W połączeniu z 12 bitami „przesunięcia w obrębie strony” od adresu liniowego, maksymalnie 52 bity są dostępne do adresowania pamięci fizycznej. Pozwala to na maksymalną konfigurację pamięci RAM wynoszącą 252 bajty lub 4 petabajty (około 4,5 × 10 15 bajtów).

Na procesorach x86-64 w natywnym trybie długim schemat translacji adresów używa PAE, ale dodaje czwartą tabelę, 512-wejściową tabelę mapowania stron poziomu 4 i rozszerza tablicę wskaźników katalogu stron do 512 wpisów zamiast oryginalnych 4 wpisów. ma w trybie chronionym. Obecnie tłumaczonych jest 48 bitów wirtualnego numeru strony, co daje wirtualną przestrzeń adresową do 256 TB. We wpisach tablicy stron w oryginalnej specyfikacji zaimplementowano 40 bitów fizycznego numeru strony.

- Struktury tablic stron

Wsparcie sprzętowe

Oprogramowanie może identyfikować za pomocą flagi CPUID PAE , czy procesor obsługuje tryb PAE, czy nie. Dostępny jest bezpłatny program dla systemu Microsoft Windows, który zawiera listę wielu możliwości procesora, w tym obsługę PAE. W systemie Linux polecenia takie jak cat /proc/cpuinfo mogą wyświetlać flagę pae , jeśli jest obecna, podobnie jak inne narzędzia, takie jak narzędzie do wykrywania sprzętu SYSLINUX .

Do uruchomienia procesora w trybie PAE wymagana jest obsługa systemu operacyjnego . Aby korzystać z PAE w celu uzyskania dostępu do więcej niż 4 GB pamięci RAM, wymagane jest dodatkowe wsparcie w systemie operacyjnym, chipsecie i płycie głównej. Niektóre chipsety nie obsługują adresów pamięci fizycznej powyżej 4 GB (FFFFFFFF w systemie szesnastkowym), a niektóre płyty główne po prostu nie mają wystarczającej liczby gniazd pamięci RAM, aby umożliwić instalację więcej niż 4 GB pamięci RAM. Niemniej jednak, nawet jeśli nie więcej niż 4 GB pamięci RAM jest dostępne i dostępne, procesor obsługujący PAE może działać w trybie PAE, na przykład w celu umożliwienia korzystania z funkcji Brak wykonywania .

Obsługa systemu operacyjnego

Microsoft Windows

32-bitowe wersje systemu Microsoft Windows obsługują PAE, jeśli są uruchamiane z odpowiednią opcją. Według specjalisty Microsoft Technical Fellow, Marka Russinovicha , niektóre sterowniki okazały się niestabilne po napotkaniu fizycznych adresów powyżej 4 GB.

W poniższej tabeli przedstawiono limity pamięci dla 32-bitowych wersji systemu Microsoft Windows:

| Wersja Windowsa | Limit pamięci |

|---|---|

| Windows 2000 Professional, serwer | 4GB |

| Zaawansowany serwer Windows 2000 | 8 GB |

| Centrum danych Windows 2000 | 32 GB |

| Windows XP Starter | 0,5 GB |

| Windows XP (inne edycje) | 4GB |

| Windows Server 2003 Web SP2 | 2 GB |

| Windows Server 2003 Standard SP2 | 4GB |

| Windows Server 2003 Enterprise/Datacenter SP2 | 64 GB |

| Windows Storage Server 2003 Enterprise | 8 GB |

| Windows Storage Server 2003 (inne wersje) | 4GB |

| Serwer Windows Home | 4GB |

| Windows Vista Starter | 1 GB |

| Windows Vista (inne wersje) | 4GB |

| Windows Server 2008 Standard, Web | 4GB |

| Windows Server 2008 Enterprise, centrum danych | 64 GB |

| Windows 7 Starter | 2 GB |

| Windows 7 (inne wersje) | 4GB |

| Windows 8 (wszystkie wersje) | 4GB |

| Windows 10 (wszystkie wersje) | 4GB |

Oryginalne wersje systemów Windows XP i Windows XP z dodatkiem SP1 wykorzystywały tryb PAE, aby umożliwić rozszerzenie pamięci RAM poza limit adresu 4 GB. Doprowadziło to jednak do problemów ze zgodnością ze sterownikami innych firm, co skłoniło Microsoft do usunięcia tej możliwości w systemie Windows XP z dodatkiem Service Pack 2. Windows XP SP2 i nowsze domyślnie na procesorach z opcją no-execute (NX) lub Execute- disable ( XD ) funkcja, działa w trybie PAE, aby umożliwić NX. Bit NX znajduje się w bicie 63 wpisu tablicy stron, a bez PAE wpisy tablicy stron w systemach 32-bitowych mają tylko 32 bity; dlatego do korzystania z funkcji NX wymagany jest tryb PAE. Jednak „klienckie” wersje 32-bitowego systemu Windows (Windows XP SP2 i nowsze, Windows Vista, Windows 7) ograniczają fizyczną przestrzeń adresową do pierwszych 4 GB w celu zapewnienia zgodności sterowników, mimo że te wersje działają w trybie PAE, jeśli włączona jest obsługa NX .

Windows 8 i nowsze wersje będą działać tylko na procesorach obsługujących PAE, oprócz NX i SSE2 .

System operacyjny Mac

Mac OS X Tiger do Mac OS X Snow Leopard obsługują PAE i bit NX na procesorach IA-32; Snow Leopard był ostatnią wersją obsługującą procesory IA-32. Na procesorach x86-64 wszystkie wersje systemu macOS używają 4-poziomowego stronicowania (stronicowanie IA-32e zamiast PAE) do adresowania pamięci powyżej 4 GB. Systemy Mac Pro i Xserve mogą wykorzystywać do 64 GB pamięci RAM.

Linuks

Jądro Linuksa zawiera pełną obsługę trybu PAE począwszy od wersji 2.3.23, w 1999 roku umożliwiając dostęp do 64 GB pamięci na maszynach 32-bitowych. Jądro Linuksa obsługujące PAE wymaga, aby procesor również obsługiwał PAE. Jądro Linuksa obsługuje PAE jako opcję kompilacji, a główne dystrybucje zapewniają jądro PAE jako opcję domyślną lub opcjonalną.

Funkcja bitowa NX wymaga jądra zbudowanego z obsługą PAE.

Dystrybucje Linuksa obecnie powszechnie używają jądra z obsługą PAE jako domyślnego, trend ten rozpoczął się w 2009 roku. Od 2012 roku wiele, w tym Ubuntu (i pochodne, takie jak Xubuntu i Linux Mint ), Red Hat Enterprise Linux 6.0 i CentOS , przestało dystrybuować jądra inne niż PAE, co sprawia, że sprzęt obsługujący PAE jest obowiązkowy. Dystrybucje Linuksa wymagające PAE mogą odmówić uruchomienia na Pentium M rodziny procesorów, ponieważ nie pokazują flagi obsługi PAE w swoich informacjach o CPUID (mimo że jest to obsługiwane wewnętrznie). Można to jednak łatwo ominąć, przynajmniej w Ubuntu , za pomocą opcji forcepae .

Dystrybucje, które nadal zapewniają opcję inną niż PAE, w tym Debian (i pochodne, takie jak LMDE 2 (Linux Mint Debian Edition) ), Slackware i LXLE , zazwyczaj robią to z etykietami „i386”, „i486” lub „retro”. Artykuł Lekka dystrybucja Linuksa wymienia kilka innych, pozwalających zainstalować Linuksa na starych komputerach.

Inni

FreeBSD i NetBSD obsługują również PAE jako opcję kompilacji jądra. FreeBSD obsługuje PAE w serii 4.x począwszy od 4.9, w serii 5.x począwszy od 5.1 oraz we wszystkich wydaniach 6.x i późniejszych. Wsparcie wymaga opcji konfiguracyjnej PAE jądra . Ładowalne moduły jądra można załadować do jądra z włączonym PAE tylko wtedy, gdy moduły zostały zbudowane z włączonym PAE; moduły binarne w dystrybucjach FreeBSD nie są budowane z włączonym PAE, a zatem nie mogą być ładowane do jądra PAE. Nie wszystkie sterowniki obsługują więcej niż 4 GB pamięci fizycznej; te sterowniki nie będą działać poprawnie w systemie z PAE.

OpenBSD obsługuje PAE od 2006 roku ze standardowym jądrem GENERIC i386. GeNUA mbH wspierała wstępne wdrożenie. Od wydania 5.0 PAE wprowadzono szereg zmian, w szczególności zmiany w przetwarzaniu i386 MMU dla PMAP, patrz pmap(9).

Solaris obsługuje PAE począwszy od wersji Solaris 7. Jednak sterowniki innych firm używane z wersją 7, które nie obejmują konkretnie obsługi PAE, mogą działać nieprawidłowo lub całkowicie zawieść w systemie z PAE.

Haiku dodał wstępne wsparcie dla PAE jakiś czas po wydaniu R1 Alpha 2. Wraz z wydaniem R1 Alpha 3 PAE jest teraz oficjalnie obsługiwane.

ArcaOS ma ograniczone wsparcie dla PAE w celu tworzenia dysków RAM powyżej granicy 4 GB.

Zobacz też

- Rozszerzenie rozmiaru strony

- Otwór PCI

- PSE-36

- Architektura systemu Windows NT

- Bariera 3 GB

- Large Physical Address Extension (LPAE) – w architekturze ARM

- 5-poziomowe stronicowanie Intela

Dalsza lektura

- „Podręcznik programisty architektury Intel 64 i IA-32, tom 3A: Podręcznik programowania systemu, część 1” . Intel . 11 lutego 2014 r.

- „Rozszerzenie adresu fizycznego” . MSDN . Microsoftu . Źródło 2020-05-06 .