Drabina rezystorowa

Drabinka rezystorowa to obwód elektryczny wykonany z powtarzających się jednostek rezystorów . Poniżej omówiono dwie konfiguracje, drabinkę rezystorów łańcuchowych i drabinkę R-2R.

Drabinka R-2R to prosty i niedrogi sposób na konwersję cyfrowo-analogową , wykorzystującą powtarzalne układy precyzyjnych sieci rezystorów w konfiguracji przypominającej drabinkę . Drabinka rezystorów łańcuchowych implementuje niepowtarzalną sieć odniesienia.

Sieć drabinkowa rezystorów łańcuchowych (konwersja analogowo-cyfrowa lub ADC)

Łańcuch wielu, często jednakowo zwymiarowanych, rezystorów podłączonych między dwoma napięciami odniesienia to sieć drabinkowa rezystorów. Rezystory działają jak dzielniki napięcia między napięciami odniesienia. Każde dotknięcie struny generuje inne napięcie, które można porównać z innym napięciem : jest to podstawowa zasada flashowego ADC (przetwornika analogowo-cyfrowego). Często napięcie zamieniane jest na prąd , co umożliwia zastosowanie sieci drabinkowej R–2R.

- Wada: dla n -bitowego ADC liczba rezystorów rośnie wykładniczo , ponieważ wymagane są rezystory, podczas gdy drabinka rezystorów rośnie tylko liniowo wraz z liczbą bitów, ponieważ potrzebuje tylko rezystorów .

- Zaleta: wyższe wartości impedancji można osiągnąć przy użyciu tej samej liczby komponentów.

Sieć drabinkowa rezystorów R–2R (konwersja cyfrowo-analogowa)

0 Podstawową sieć drabinkową rezystorów R-2R pokazano na rysunku 1. Bit a n −1 (najbardziej znaczący bit, MSB) do bitu a (najmniej znaczący bit, LSB) są sterowane z cyfrowych bramek logicznych. W idealnym przypadku wejścia bitowe są przełączane między V = 0 (logika 0) a V = Vref (logika 1). Sieć R-2R powoduje, że te bity cyfrowe są ważone pod względem ich wkładu w napięcie wyjściowe Vout . W zależności od tego, które bity są ustawione na 1, a które na 0, napięcie wyjściowe ( V out ) będzie miało odpowiedni schodkowa wartość między 0 a Vref minus wartość minimalnego kroku, odpowiadająca bitowi 0. Rzeczywista wartość Vref (i napięcie logiki 0) będzie zależała od rodzaju technologii użytej do generowania sygnałów cyfrowych.

Dla wartości cyfrowej VAL przetwornika cyfrowo-analogowego R–2R z N bitami i poziomami logicznymi odniesienia 0 V/ V napięcie wyjściowe Vout wynosi :

Na przykład, jeśli N = 5 (stąd 2 N = 32) i V ref = 3,3 V (typowe napięcie logiczne CMOS 1), wtedy napięcie wyjściowe V będzie wahać się od 0 woltów (VAL = 0 = 00000 2 ) do maksimum (VAL = 31 = 11111 2 ):

ze stopniami (odpowiadającymi VAL = 1 = 00001 2 )

Drabinka R-2R jest niedroga i stosunkowo łatwa do wyprodukowania, ponieważ wymagane są tylko dwie wartości rezystorów (lub nawet jedna, jeśli R jest tworzony przez połączenie pary 2R lub jeśli 2R jest tworzony przez umieszczenie pary R w seria). Jest szybki i ma stałą impedancję wyjściową R. Drabinka R–2R działa jak ciąg dzielników prądu , których dokładność wyjściowa zależy wyłącznie od tego, jak dobrze każdy rezystor jest dopasowany do pozostałych. Małe niedokładności w rezystorach MSB mogą całkowicie przytłoczyć wkład rezystorów LSB. Może to skutkować niemonotonicznym zachowaniem na głównych skrzyżowaniach, takich jak od 01111 2 do 10000 2 . W zależności od rodzaju zastosowanych bramek logicznych i konstrukcji obwodów logicznych, na tak dużych skrzyżowaniach mogą występować przejściowe skoki napięcia, nawet przy idealnych wartościach rezystorów. Można je filtrować za pomocą pojemności w węźle wyjściowym (w konsekwencji zmniejszenie przepustowości może być znaczące w niektórych zastosowaniach). Wreszcie, rezystancja 2R jest połączona szeregowo z impedancją wyjścia cyfrowego. Bramki o wysokiej impedancji wyjściowej ( np ) może być nieodpowiednie w niektórych przypadkach. Ze wszystkich powyższych powodów (i niewątpliwie innych) ten typ przetwornika cyfrowo-analogowego jest zwykle ograniczony do stosunkowo małej liczby bitów; chociaż układy scalone mogą zwiększać liczbę bitów do 14 lub nawet więcej, bardziej typowe jest 8 bitów lub mniej.

Dokładność drabinek rezystorowych R–2R

Rezystory używane z bardziej znaczącymi bitami muszą być proporcjonalnie dokładniejsze niż te używane z mniej znaczącymi bitami; na przykład w omówionej powyżej sieci R–2R niedokładności rezystorów bit-4 (MSB) muszą być nieznaczne w porównaniu z R/32 (tj. znacznie lepsze niż 3%). Ponadto, aby uniknąć problemów przy przejściu od 10000 2 do 01111 2 , suma niedokładności w niższych bitach musi być znacznie mniejsza niż R/32. Wymagana dokładność podwaja się z każdym dodatkowym bitem: dla 8 bitów wymagana dokładność będzie lepsza niż 1/256 (0,4%). W układach scalonych , sieci R-2R o wysokiej dokładności mogą być drukowane bezpośrednio na pojedynczym podłożu przy użyciu technologii cienkowarstwowej , dzięki czemu rezystory mają podobne właściwości elektryczne . Mimo to często muszą być przycinane laserowo, aby osiągnąć wymaganą precyzję. Zademonstrowano takie wbudowane drabinki rezystorowe dla przetworników cyfrowo-analogowych osiągających 16-bitową dokładność.

Drabinka rezystorowa o nierównych szczeblach

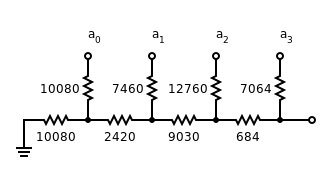

Nie jest konieczne, aby każdy „szczebel” drabiny R – 2R używał tych samych wartości rezystorów. Konieczne jest jedynie, aby wartość „2R” odpowiadała sumie wartości „R” plus równoważna Théveninowi szczebli o niższym znaczeniu. Rysunek 2 przedstawia liniowy 4-bitowy przetwornik cyfrowo-analogowy z nierównymi rezystorami.

Pozwala to na stworzenie dość dokładnego przetwornika cyfrowo-analogowego z heterogenicznej kolekcji rezystorów poprzez tworzenie przetwornika cyfrowo-analogowego po jednym bicie na raz. Na każdym etapie rezystory dla „szczebla” i „nogi” są dobierane tak, aby wartość szczebla odpowiadała wartości nogi plus równoważna rezystancja poprzednich szczebli. Rezystory szczebli i nóg można utworzyć, łącząc szeregowo lub równolegle inne rezystory w celu zwiększenia liczby dostępnych kombinacji. Proces ten można zautomatyzować.

Zobacz też

Linki zewnętrzne

- ECE209: Notatki z wykładu DAC - Ohio State University

- EE247: Przetworniki cyfrowo-analogowe — Berkeley University of California

- Uproszczone notatki z wykładów DAC/ADC — University of Michigan

- Przetworniki cyfrowo-analogowe (slajdy) - Georgia Tech

- Samouczek MT-014: Ciągowe przetworniki cyfrowo-analogowe i w pełni dekodowane przetworniki cyfrowo-analogowe - urządzenia analogowe

- Samouczek MT-015: Binarne przetworniki cyfrowo- analogowe - urządzenia analogowe

- Samouczek MT-016: Segmentowe przetworniki cyfrowo- analogowe - urządzenia analogowe

- Samouczek MT-018: Celowo nieliniowe przetworniki cyfrowo-analogowe - urządzenia analogowe

- Rezystorowe sieci drabinkowe R2R — BI Technologies

- Nota aplikacyjna dotycząca sieci drabinkowych R/2R — TT Electronics