Integralność sygnału

Integralność sygnału lub SI to zestaw miar jakości sygnału elektrycznego . W elektronice cyfrowej strumień wartości binarnych jest reprezentowany przez przebieg napięcia (lub prądu). Jednak sygnały cyfrowe mają zasadniczo analogowy , a wszystkie sygnały podlegają efektom, takim jak szum , zniekształcenia i straty. Na krótkich dystansach i przy niskich przepływnościach prosty przewodnik może transmitować to z wystarczającą wiernością. Przy wysokich przepływnościach a na dłuższych dystansach lub za pośrednictwem różnych mediów różne efekty mogą pogorszyć sygnał elektryczny do punktu, w którym występują błędy i awaria systemu lub urządzenia. Zadaniem inżynierii integralności sygnału jest analiza i łagodzenie tych skutków. Jest to ważna czynność na wszystkich poziomach pakowania i montażu elektroniki, od wewnętrznych połączeń układu scalonego (IC), poprzez opakowanie , płytkę drukowaną (PCB), płytę montażową i połączeń międzysystemowych. Chociaż istnieją pewne wspólne tematy na tych różnych poziomach, istnieją również względy praktyczne, w szczególności czas przelotu międzysieciowego w porównaniu z okresem bitowym, które powodują znaczne różnice w podejściu do integralności sygnału dla połączeń on-chip w porównaniu z połączeniami chip-to-chip .

Niektóre z głównych problemów związanych z integralnością sygnału to dzwonienie , przesłuch , odbicie od podłoża , zniekształcenia , utrata sygnału i szum zasilania .

Historia

Integralność sygnału obejmuje przede wszystkim parametry elektryczne przewodów i innych struktur opakowaniowych używanych do przenoszenia sygnałów w produkcie elektronicznym. Taka wydajność jest kwestią podstawowej fizyki i jako taka pozostała stosunkowo niezmieniona od początku sygnalizacji elektronicznej. Pierwszy transatlantycki kabel telegraficzny miał poważne problemy z integralnością sygnału , a analiza problemów przyniosła wiele narzędzi matematycznych nadal używanych do analizy problemów z integralnością sygnału, takich jak równania telegrafisty . Produkty tak stare jak Western Electric poprzeczna centrala telefoniczna (około 1940 r.), oparta na przekaźniku drutowo-sprężynowym, ucierpiała na prawie wszystkich skutkach obserwowanych dzisiaj - dzwonieniu, przesłuchach, odbijaniu od podłoża i szumach zasilania, które są plagą nowoczesnych produktów cyfrowych.

Na płytkach drukowanych integralność sygnału stała się poważnym problemem, gdy czasy przejścia (narastania i opadania) sygnałów zaczęły być porównywalne z czasem propagacji na płytce. Z grubsza mówiąc, dzieje się tak zwykle, gdy prędkości systemu przekraczają kilkadziesiąt MHz. Na początku tylko kilka najważniejszych sygnałów o największej szybkości wymagało szczegółowej analizy lub zaprojektowania. Wraz ze wzrostem prędkości coraz większa część sygnałów wymagała analizy SI i praktyk projektowych. W nowoczesnych (> 100 MHz) projektach obwodów zasadniczo wszystkie sygnały muszą być projektowane z myślą o SI.

W przypadku układów scalonych analiza SI stała się konieczna ze względu na ograniczone zasady projektowania. We wczesnych latach współczesnej ery VLSI projektowanie i układ cyfrowych układów scalonych były procesami ręcznymi. Wykorzystanie abstrakcji i zastosowanie technik automatycznej syntezy umożliwiło od tego czasu projektantom wyrażanie swoich projektów przy użyciu języków wysokiego poziomu i stosowanie zautomatyzowanego procesu projektowania do tworzenia bardzo złożonych projektów, ignorując w dużym stopniu charakterystykę elektryczną podstawowych obwodów. Jednak skalowanie trendów (patrz prawo Moore'a ) przywrócił efekty elektryczne na pierwszy plan w najnowszych węzłach technologicznych. Przy skalowaniu technologii poniżej 0,25 µm opóźnienia drutów stały się porównywalne lub nawet większe niż opóźnienia bramek. W rezultacie, aby osiągnąć zamknięcie czasowe, należało wziąć pod uwagę opóźnienia przewodów . W technologiach nanometrowych o wielkości 0,13 µm i mniejszej niezamierzone interakcje między sygnałami (np. przesłuch) stały się ważnym elementem projektowania cyfrowego. W tych węzłach technologicznych nie można zapewnić wydajności i poprawności projektu bez uwzględnienia wpływu hałasu.

Większość tego artykułu dotyczy SI w odniesieniu do nowoczesnej technologii elektronicznej - w szczególności zastosowania układów scalonych i technologii płytek drukowanych . Niemniej jednak zasady SI nie dotyczą wyłącznie stosowanej technologii sygnalizacyjnej. SI istniał na długo przed pojawieniem się obu technologii i będzie istniał tak długo, jak długo będzie istniała komunikacja elektroniczna.

Integralność sygnału na chipie

Problemy z integralnością sygnału w nowoczesnych układach scalonych (IC) mogą mieć wiele drastycznych konsekwencji dla projektów cyfrowych:

- Produkty mogą w ogóle nie działać lub, co gorsza, stać się zawodne w terenie.

- Projekt może działać, ale tylko przy prędkościach wolniejszych niż planowano

- Wydajność może być obniżona, czasami drastycznie

Koszt tych awarii jest bardzo wysoki i obejmuje koszty fotomaski , koszty inżynieryjne i koszty alternatywne wynikające z opóźnionego wprowadzenia produktu. Dlatego opracowano narzędzia do automatyzacji projektowania elektronicznego (EDA) do analizy, zapobiegania i korygowania tych problemów. W układach scalonych lub układach scalonych główną przyczyną problemów z integralnością sygnału jest przesłuch . W CMOS wynika to przede wszystkim z pojemności sprzężenia , ale ogólnie może być spowodowane indukcyjnością wzajemną , sprzężenie substratu , nieidealne działanie bramki i inne źródła. Poprawki zwykle polegają na zmianie rozmiarów sterowników i/lub rozstawu przewodów.

W obwodach analogowych projektanci zajmują się również szumami pochodzącymi ze źródeł fizycznych, takimi jak szum termiczny , szum migotania i szum śrutu . Te źródła szumu z jednej strony wyznaczają dolną granicę najmniejszego sygnału, który można wzmocnić, az drugiej strony określają górną granicę użytecznego wzmocnienia.

W cyfrowych układach scalonych szum w sygnale będącym przedmiotem zainteresowania powstaje głównie w wyniku sprzężenia efektów przełączania innych sygnałów. Rosnąca gęstość połączeń międzysieciowych doprowadziła do tego, że każdy przewód ma sąsiadów, którzy są fizycznie bliżej siebie, co prowadzi do zwiększonego przesłuchu między sąsiednimi sieciami. Ponieważ obwody nadal kurczą się zgodnie z prawem Moore'a , kilka efektów sprzysięgło się, aby pogorszyć problemy z hałasem:

- Aby utrzymać znośny opór pomimo zmniejszonej szerokości, nowoczesne geometrie drutów są grubsze proporcjonalnie do ich rozstawu. Zwiększa to pojemność ściany bocznej kosztem pojemności do masy, a tym samym zwiększa indukowane napięcie szumu (wyrażone jako ułamek napięcia zasilania).

- Skalowanie technologii doprowadziło do obniżenia napięć progowych dla tranzystorów MOS, a także zmniejszyło różnicę między napięciami progowymi i zasilającymi, zmniejszając w ten sposób marginesy szumów .

- Prędkości logiki, aw szczególności prędkości zegara, znacznie wzrosły, co prowadzi do krótszych czasów przejścia (narastania i opadania). Te krótsze czasy przejścia są ściśle związane z wyższym przesłuchem pojemnościowym. Również przy tak dużych prędkościach w grę wchodzą właściwości indukcyjne drutów, a zwłaszcza indukcyjność wzajemna.

Efekty te zwiększyły interakcje między sygnałami i zmniejszyły odporność na zakłócenia cyfrowych obwodów CMOS. Doprowadziło to do tego, że szumy są poważnym problemem dla cyfrowych układów scalonych, który musi wziąć pod uwagę każdy projektant chipów cyfrowych przed rozpoczęciem nagrywania . Istnieje kilka obaw, które należy złagodzić:

- Zakłócenia mogą spowodować, że sygnał przyjmie niewłaściwą wartość. Jest to szczególnie krytyczne, gdy sygnał ma zostać zablokowany (lub próbkowany), ponieważ do elementu pamięci może zostać załadowana niewłaściwa wartość, powodując błąd logiczny.

- Szumy mogą opóźniać ustalenie się sygnału do prawidłowej wartości. Nazywa się to często opóźnieniem szumu .

- Hałas (np. dzwonienie) może spowodować spadek napięcia wejściowego bramki poniżej poziomu gruntu lub przekroczenie napięcia zasilania. Może to skrócić żywotność urządzenia poprzez naprężenie komponentów, wywołać zatrzaśnięcie lub spowodować wielokrotne przełączanie sygnałów, które powinny zmieniać się tylko raz w danym okresie.

Znajdowanie problemów z integralnością sygnału IC

Zazwyczaj projektant układów scalonych podjąłby następujące kroki w celu weryfikacji SI:

- Wykonaj ekstrakcję układu , aby uzyskać pasożyty powiązane z układem. Zwykle w symulacjach wyodrębnia się pasożyty z najgorszego i najlepszego przypadku pasożytów i wykorzystuje je w symulacjach. W przypadku układów scalonych, w przeciwieństwie do PCB, fizyczny pomiar pasożytów prawie nigdy nie jest wykonywany, ponieważ pomiary in situ za pomocą zewnętrznego sprzętu są niezwykle trudne. Co więcej, wszelkie pomiary miałyby miejsce po utworzeniu chipa, co jest zbyt późne, aby naprawić zaobserwowane problemy.

- Utwórz listę oczekiwanych zdarzeń związanych z hałasem, w tym różne rodzaje hałasu, takie jak sprzężenie i współdzielenie ładunku .

- Utwórz model dla każdego zdarzenia akustycznego. Bardzo ważne jest, aby model był tak dokładny, jak to konieczne do modelowania danego zdarzenia akustycznego.

- Dla każdego zdarzenia sygnałowego zdecyduj, jak wzbudzić obwód, aby wystąpiło zdarzenie szumowe.

- Utwórz listę sieci SPICE (lub innego symulatora obwodu) , która reprezentuje pożądane wzbudzenie, aby uwzględnić tyle efektów (takich jak pasożytnicza indukcyjność i pojemność oraz różne efekty zniekształceń), ile potrzeba.

- Uruchom symulacje SPICE. Przeanalizuj wyniki symulacji i zdecyduj, czy konieczne jest przeprojektowanie. Powszechne jest analizowanie wyników za pomocą wzoru oczu i obliczania budżetu czasowego.

Nowoczesne narzędzia integralności sygnału do projektowania układów scalonych wykonują wszystkie te kroki automatycznie, generując raporty, które zapewniają projektowi czysty stan zdrowia lub listę problemów, które należy naprawić. Jednak takie narzędzia na ogół nie są stosowane w całym układzie scalonym, a jedynie w wybranych sygnałach zainteresowania.

Naprawianie problemów z integralnością sygnału IC

Po znalezieniu problemu należy go naprawić. Typowe rozwiązania problemów z układem scalonym na chipie obejmują:

- Usuwanie nieciągłości impedancji. Znalezienie miejsc, w których występują znaczne przesunięcia impedancji i dostosowanie geometrii ścieżki w celu przesunięcia impedancji, aby lepiej pasowała do reszty ścieżki.

- Optymalizacja sterownika. Możesz mieć za dużo napędu, ale też za mało.

- Wstawienie bufora. W tym podejściu, zamiast zwiększania rozmiaru sterownika ofiary, w odpowiednim punkcie sieci ofiary wstawiany jest bufor.

- Redukcja agresora. Działa to poprzez zwiększenie czasu przejścia sieci atakującej poprzez zmniejszenie siły jej kierowcy.

- Dodaj ekranowanie. Dodaj ekranowanie krytycznych sieci lub sieci zegarowych za pomocą ekranów GND i VDD, aby zredukować efekt przesłuchu (ta technika może prowadzić do narzutu routingu).

- tras . Zmiany trasowania mogą być bardzo skuteczne w rozwiązywaniu problemów związanych z hałasem, głównie poprzez zmniejszenie najbardziej kłopotliwych efektów sprzężenia poprzez separację.

Każda z tych poprawek może powodować inne problemy. Problemy tego typu należy rozwiązywać w ramach przepływów projektowych i zamknięcia projektu . Ponowna analiza po zmianach projektowych jest rozsądnym środkiem.

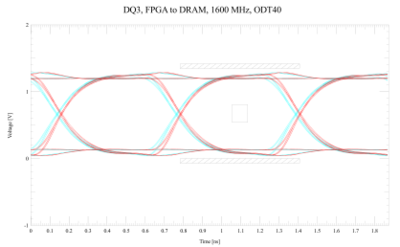

Zakończenie na bieżąco

Zakończenie na matrycy (ODT) lub impedancja sterowana cyfrowo (DCI) to technologia, w której rezystor końcowy do dopasowania impedancji w liniach transmisyjnych jest umieszczony w chipie półprzewodnikowym, zamiast oddzielnego, dyskretnego urządzenia zamontowanego na płytce drukowanej. Bliskość zakończenia od odbiornika skraca odgałęzienie między nimi, poprawiając w ten sposób ogólną integralność sygnału.

Integralność sygnału między chipami

W przypadku połączeń przewodowych ważne jest porównanie czasu przelotu połączenia międzysieciowego z okresem bitowym, aby zdecydować, czy potrzebne jest połączenie o dopasowanej impedancji, czy bez.

Czas lotu kanału (opóźnienie) interkonektu wynosi około 1 ns na 15 cm ( 6 cali ) linii paskowej FR-4 (prędkość propagacji zależy od dielektryka i geometrii). Odbicia poprzednich impulsów przy niedopasowaniach impedancji zanikają po kilku odbiciach w górę iw dół linii (tj. w kolejności czasu przelotu). Przy niskich przepływnościach echa same zanikają, a w połowie impulsu nie stanowią problemu. Dopasowanie impedancji nie jest ani konieczne, ani pożądane. Istnieje wiele typów płytek drukowanych innych niż FR-4, ale zwykle są one bardziej kosztowne w produkcji.

Delikatna tendencja do wyższych przepływności gwałtownie przyspieszyła w 2004 roku wraz z wprowadzeniem przez firmę Intel standardu PCI-Express . Idąc tym tropem, większość standardów połączeń typu chip-to-chip przeszła architektoniczną zmianę z magistrali równoległych na łącza serializatora/deserializatora ( SERDES ) zwane „pasami”. Takie łącza szeregowe eliminują przekrzywienie zegara magistrali równoległej i zmniejszają liczbę ścieżek oraz wynikające z nich efekty sprzężenia, ale zalety te wiążą się z dużym wzrostem przepływności na liniach i krótszymi okresami bitowymi.

Przy szybkości transmisji danych rzędu wielu gigabitów/s projektanci łączy muszą wziąć pod uwagę odbicia przy zmianach impedancji (np. tam, gdzie ślady zmieniają poziomy na przelotkach , patrz Linie transmisyjne ), szum wywołany przez gęsto upakowane sąsiednie połączenia ( przesłuch ) oraz tłumienie wysokich częstotliwości spowodowane efektem naskórkowości w śladzie metalu i stycznej strat dielektrycznych. Przykłady technik łagodzenia tych upośledzeń to przeprojektowanie geometrii przelotki w celu zapewnienia dopasowania impedancji, odpowiednio użycie sygnalizacji różnicowej i filtrowania z preemfazą .

Przy tych nowych przepływnościach multigigabit/s okres bitowy jest krótszy niż czas lotu; echa poprzednich impulsów mogą dotrzeć do odbiornika na szczycie głównego impulsu i uszkodzić go. W inżynierii komunikacyjnej nazywa się to interferencją międzysymbolową (ISI). W inżynierii integralności sygnału jest to zwykle nazywane zamknięciem oka (odniesienie do bałaganu w środku rodzaju śladu oscyloskopu zwanego diagramem oka). Gdy okres bitu jest krótszy niż czas lotu, eliminacja odbić za pomocą klasycznych technik mikrofalowych, takich jak dopasowanie impedancji elektrycznej nadajnika do interkonektu, odcinków interkonektu względem siebie oraz interkonektu do odbiornika ma kluczowe znaczenie. Zakończenie ze źródłem lub obciążeniem jest synonimem dopasowania na dwóch końcach. Impedancja interkonektu, którą można wybrać, jest ograniczona impedancją wolnej przestrzeni ( ~377 Ω ), geometrycznym współczynnikiem kształtu i pierwiastkiem kwadratowym względnej stałej dielektrycznej wypełniacza linii paskowej (zwykle FR-4, ze względną stałą dielektryczną z ~4). Wszystkie te właściwości określają impedancję charakterystyczną ścieżki . 50 omów jest wygodnym wyborem dla linii z jednym końcem i 100 omów dla różnic.

W wyniku niskiej impedancji wymaganej do dopasowania, ścieżki sygnałowe PCB przenoszą znacznie więcej prądu niż ich odpowiedniki na chipie. Ten większy prąd indukuje przesłuch głównie w trybie magnetycznym lub indukcyjnym, w przeciwieństwie do trybu pojemnościowego. Aby zwalczyć ten przesłuch, projektanci cyfrowych obwodów drukowanych muszą być świadomi nie tylko zamierzonej ścieżki sygnału dla każdego sygnału, ale także ścieżki powracającego prądu sygnału dla każdego sygnału. Sam sygnał i jego ścieżka prądu powracającego sygnału są równie zdolne do generowania przesłuchu indukcyjnego. Różnicowe pary śladowe pomagają zredukować te efekty.

Trzecia różnica między połączeniem on-chip i chip-to-chip dotyczy rozmiaru przekroju poprzecznego przewodu sygnałowego, a mianowicie tego, że przewody PCB są znacznie większe (zwykle mają szerokość 100 µm lub więcej). Zatem ścieżki PCB mają małą rezystancję szeregową (zwykle 0,1 Ω/cm) przy DC. Składowa impulsu o wysokiej częstotliwości jest jednak tłumiona przez dodatkową rezystancję spowodowaną efektem naskórkowania i styczną stratności dielektrycznej związaną z materiałem PCB.

Główne wyzwanie często zależy od tego, czy projekt jest aplikacją konsumencką opartą na kosztach, czy aplikacją infrastrukturalną opartą na wydajności. Zwykle wymagają one obszernej weryfikacji po rozplanowaniu (za pomocą symulatora EM ) i optymalizacji projektu przed rozplanowaniem (za pomocą SPICE i symulatora kanałów).

Topologia routingu

Poziomy szumów w ścieżce/sieci w dużym stopniu zależą od wybranej topologii routingu. W topologii punkt-punkt sygnał jest kierowany z nadajnika bezpośrednio do odbiornika (jest to stosowane w PCIe , RapidIO , Gigabit Ethernet , DDR2 / DDR3 / DDR4 DQ/DQS itp.). Topologia punkt-punkt ma najmniej problemów z SI, ponieważ nie ma dużych dopasowań impedancji wprowadzanych przez linię T (dwukierunkowy podział ścieżki).

W przypadku interfejsów, w których wiele pakietów jest odbieranych z tej samej linii (na przykład z konfiguracją płyty montażowej), linia musi zostać w pewnym momencie podzielona, aby obsłużyć wszystkie odbiorniki. Uważa się, że występują pewne odgałęzienia i niedopasowania impedancji. Wielopakietowe interfejsy obejmują B LVDS , DDR2/DDR3/DDR4 C/A bank, RS485 i CAN Bus . Istnieją dwie główne topologie wielopakietowe: drzewo i przelot.

Znajdowanie problemów z integralnością sygnału

- Wykonaj ekstrakcję układu , aby uzyskać pasożyty powiązane z układem. Zwykle w symulacjach wyodrębnia się pasożyty z najgorszego i najlepszego przypadku pasożytów i wykorzystuje je w symulacjach. Ze względu na rozproszony charakter wielu upośledzeń, do ekstrakcji wykorzystuje się symulację elektromagnetyczną.

- Jeśli płytka drukowana lub obudowa już istnieje, projektant może również zmierzyć uszkodzenie wynikające z połączenia za pomocą szybkiego oprzyrządowania, takiego jak wektorowy analizator sieci . Na przykład grupa zadaniowa IEEE P802.3ap wykorzystuje zmierzone parametry S jako przypadki testowe dla proponowanych rozwiązań problemu Ethernetu 10 Gbit/s na płytach montażowych.

- Dokładne modelowanie hałasu jest koniecznością. Utwórz listę oczekiwanych zdarzeń związanych z hałasem, w tym różnych rodzajów hałasu, takich jak sprzężenie i współdzielenie ładunku . Specyfikacja informacji o buforze wejściowym i wyjściowym (IBIS) lub modele obwodów mogą być używane do reprezentowania sterowników i odbiorników.

- Dla każdego zdarzenia szumowego zdecyduj, jak wzbudzić obwód, aby zdarzenie szumowe wystąpiło.

- Utwórz listę sieci SPICE (lub innego symulatora obwodu) , która reprezentuje pożądane wzbudzenie.

- Uruchom SPICE i zapisz wyniki.

- Przeanalizuj wyniki symulacji i zdecyduj, czy konieczne jest przeprojektowanie. Aby przeanalizować wyniki, dość często generowane jest oko danych i obliczany jest budżet czasowy. Przykładowy film przedstawiający generowanie oka danych można znaleźć w serwisie YouTube: An Eye is Born .

Istnieją specjalne narzędzia EDA , które pomagają inżynierowi wykonać wszystkie te kroki na każdym sygnale w projekcie, wskazując problemy lub sprawdzając, czy projekt jest gotowy do produkcji. Wybierając najlepsze narzędzie do określonego zadania, należy wziąć pod uwagę cechy każdego z nich, takie jak pojemność (ile węzłów lub elementów), wydajność (szybkość symulacji), dokładność (jak dobre są modele), zbieżność (jak dobry jest solver). ), możliwości (nieliniowe kontra liniowe, zależne od częstotliwości kontra niezależne od częstotliwości itp.) oraz łatwość użytkowania.

Naprawianie problemów z integralnością sygnału

Projektant pakietu IC lub PCB usuwa problemy z integralnością sygnału za pomocą następujących technik:

- Umieszczenie solidnej płaszczyzny odniesienia w sąsiedztwie śladów sygnału w celu kontrolowania przesłuchu

- Kontrolowanie odstępów szerokości ścieżki od płaszczyzny odniesienia w celu uzyskania spójnej impedancji ścieżki

- Używanie zakończeń do kontrolowania dzwonienia

- Prowadź ścieżki prostopadle na sąsiednich warstwach, aby zredukować przesłuch

- Zwiększenie odstępów między ścieżkami w celu zmniejszenia przesłuchu

- Zapewnienie wystarczających połączeń uziemienia (i zasilania), aby ograniczyć odbijanie się masy (ta podkategoria integralności sygnału jest czasami nazywana oddzielnie jako integralność zasilania )

- Dystrybucja mocy za pomocą solidnych warstw płaskich w celu ograniczenia szumów zasilania

- filtra preemfazy do komórki napędowej nadajnika

- Dodanie korektora do komórki odbiorczej

- Ulepszony zegar i obwody odzyskiwania danych (CDR) z niskim jitterem/szumem fazowym

Każda z tych poprawek może powodować inne problemy. Problemy tego typu należy rozwiązywać w ramach przepływów projektowych i zamknięcia projektu .

Zobacz też

Notatki

- Howarda Johnsona; Marcina Grahama. (2002). Szybka propagacja sygnału: zaawansowana czarna magia . Upper Saddle River, New Jersey: Prentice Hall PTR. ISBN 0-13-084408-X . Tekst referencyjny na poziomie zaawansowanym dla doświadczonych projektantów cyfrowych, którzy chcą docisnąć swoje projekty do górnych granic prędkości i odległości.

- Eryk Bogatin. (2009). Integralność sygnału i zasilania — uproszczona, wydanie drugie . Upper Saddle River, New Jersey: Prentice Hall. ISBN 978-0-13-234979-6 . Zarchiwizowane od oryginału w dniu 2011-09-10. Z tylnej okładki: Czerpie z przemysłowego doświadczenia autora i jego pracy w nauczaniu ponad pięciu tysięcy inżynierów.

- Stephena H. Halla; Garrett W. Hall; Jamesa A. McCalla. (2000). Projektowanie systemów cyfrowych o dużej szybkości: podręcznik teorii połączeń i praktyk projektowych . Nowy Jork: Wiley. ISBN 0-471-36090-2 .

- Williama J. Dally'ego; Johna W. Poultona. (1999). Inżynieria systemów cyfrowych . Cambridge: Uniwersytet Cambridge. Naciskać. ISBN 0-521-59292-5 . Podręcznik dotyczący problemów budowy systemów cyfrowych, w tym integralności sygnału.

- Douglasa Brooksa. (2003). Problemy z integralnością sygnału i projektowanie płytek drukowanych . Upper Saddle River, New Jersey: Prentice Hall PTR. ISBN 0-13-141884-X . Ta książka omawia zasady elektrotechniki i integralności sygnału od podstawowego poziomu, zakładając niewielkie wcześniejsze zrozumienie.

- Geoff Lawday; Davida Irelanda i Grega Edlunda. (2008). Towarzysz inżyniera integralności sygnału: testy i pomiary w czasie rzeczywistym oraz symulacja projektowania . Upper Saddle River, New Jersey: Prentice Hall. ISBN 978-0-13-186006-3 .

- Raj; A. Ege Engin. (2008). Modelowanie i projektowanie integralności mocy dla półprzewodników i systemów . Upper Saddle River, New Jersey: Prentice Hall. ISBN 978-0-13-615206-4 . Wykorzystując realistyczne studia przypadków i przykłady oprogramowania do pobrania, dwóch czołowych ekspertów demonstruje najlepsze dzisiejsze techniki projektowania i modelowania połączeń w celu efektywnego rozdziału mocy i minimalizacji szumów. Autorzy starannie przedstawiają podstawowe koncepcje projektowania dystrybucji mocy, systematycznie prezentują i porównują wiodące techniki modelowania szumów oraz łączą te techniki z konkretnymi zastosowaniami. Ich liczne przykłady obejmują zarówno najprostsze (wykorzystujące równania analityczne do obliczania szumów zasilania), jak i złożone aplikacje na poziomie systemu.

- Integralność sygnału dla projektantów PCB

- Centrum integralności sygnału Altera

- Podstawowe zasady integralności sygnału

- Agilent EEsof EDA — zasoby do analizy integralności sygnału

- „Wskazówka projektowa: Modeluj instrumenty, aby poprawić symulację integralności sygnału”, EETimes , John Olah, 2007-październik-25

- Tematy integralności sygnału były omawiane na DesignCon 2008 od 4 lutego 2008 do 7 lutego 2008

- „Zrozumienie integralności sygnału — integralność sygnału staje się coraz większym problemem wraz ze wzrostem częstotliwości zegara” — Eric Bogatin, GigaTest Labs, Agilent Application Note 5988-5978EN, kwiecień 2002, 8 stron, PDF, 0,9 MB

- „Seria analizy integralności sygnału, część 1: jednoportowy TDR, TDR/TDT i 2-portowy TDR” (Agilent Application Note 5989-5763EN, luty 2007, 72 strony, PDF, 5,2 MB)

- „Seria analiz integralności sygnału, część 2: 4-portowy TDR/VNA/PLTS” (Agilent Application Note 5989-5764EN, luty 2007, 56 stron, PDF, 3,6 MB)

- „Seria analiz integralności sygnału, część 3: ABC usuwania osadzania” (Agilent Application Note 5989-5765EN, lipiec 2007, 48 stron, PDF, 2,5 MB)