MOS Technology Agnus

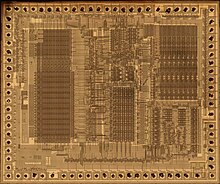

Technologia MOS „Agnus” , zwykle nazywana Agnus , jest układem scalonym w niestandardowym chipsecie komputera Amiga . Chipy Agnus , Denise i Paula wspólnie utworzyły chipsety OCS i ECS .

Agnus to Chip Generatora Adresów. Jego główną funkcją w obszarze układu scalonego jest RAM i Enkoder Adresów Rejestrów, który obsługuje wszystkie adresy DMA . 8361 Agnus składa się z około 21 000 tranzystorów i zawiera kontrolery kanałów DMA. Według Jaya Minera , oryginalny Agnus został wyprodukowany w procesie produkcyjnym 5 μm, podobnie jak wszystkie chipsety OCS . Znajdują się tu również Blitter i Copper .

Cechy Agnusa:

- Blitter , manipulator map bitowych . Blitter jest w stanie kopiować bloki wyświetlanych danych lub dowolne dane w pamięci wbudowanej z dużą prędkością z różnymi operacjami rastrowymi, a także rysować linie o doskonałej jakości co do piksela i wypełniać zarysowane wielokąty, jednocześnie uwalniając procesor do równoczesnych zadań.

- „ Copper ”, koprocesor synchronizujący wyświetlacz

- 25 kanałów bezpośredniego dostępu do pamięci (DMA), umożliwiających korzystanie z grafiki, dźwięku i wejścia/wyjścia przy minimalnej interwencji procesora

- Kontroler odświeżania DRAM

- Kontroler pamięci (pamięć, do której dostęp ma procesor i chipset)

- Generuje zegar systemowy z oscylatora 28 MHz

- Czas wideo

Agnus został zastąpiony przez Alice w Amidze 4000 i Amidze 1200 , kiedy chipset AGA został wprowadzony w 1992 roku.

Żetony według możliwości

-

OCS Agnus , który może zaadresować do 512 kB pamięci Chip RAM (wersje PLCC dodają 512 kB pseudoszybkiej pamięci RAM)

- 8361 ( DIP ) - Amiga 1000 (NTSC); Amiga 2000 model A (NTSC)

- 8367 (DIP) - Amiga 1000 (PAL); Amiga 2000 model A (PAL)

- 8370 ( PLCC ) - Amiga 500 do wersji 5.x (NTSC); Amiga 2000 model B do wersji 4.5 (NTSC)

- 8371 ( PLCC ) - Amiga 500 do wersji 5.x (PAL); Amiga 2000 model B do wersji 4.5 (PAL)

-

ECS Agnus , który może zaadresować do 1 MB pamięci Chip RAM

- 8372 - brak danych*

- 8372A - Amiga 500 od wersji 6 (NTSC/PAL); Amiga 2000 model B od wersji 6.0 do wersji 6.3 (NTSC/PAL); Commodore CDTV

- 8375 (tylko 318069-16) (PAL) - Amiga 500 od wersji 6 (PAL); Amiga 2000 model B od wersji 6.4 (PAL)

- 8375 (tylko 318069-17) (NTSC) - Amiga 500 od wersji 6 (NTSC); Amiga 2000 model B od wersji 6.4 (NTSC)

-

ECS Agnus , który może zaadresować do 2 MB pamięci Chip RAM

- 8372AB - Amiga 3000 od wersji 6.1 do wersji 8.9 (NTSC/PAL)

- 8372B — Amiga 3000 Rev 9 (NTSC/PAL)

- 8375 (PAL) - Amiga 500 Plus ; Amiga 600 (PAL)

- 8375 (NTSC) — Amiga 600 (NTSC)

* Gdzieś 8372A Agnus wymieniony jako po prostu „8372”.

Chipsy w paczce

- 48-odprowadzeniowy DIP Agnus (znany również jako cienki Agnus ): 8361; 8367

- 84-stykowy PLCC Fat Agnus (nazywany Fat Lady na większości płyt głównych Amigi 2000) 8370; 8371; 8372; 8372A; 8372AB; 8372B; 8375

Uwagi Fat Agnus 1MB i Fat Agnus 2MB, zwykle znane jako Super Agnus; Super Gruby Agnus; Grubszy Agnus; Wielki Agnus; Big Fat Agnus, ale to nie są oficjalne nazwy.

Kanały DMA

| Priorytet | Nazwa | Liczyć | Cykle/Rasterline | Żeton | Notatki |

|---|---|---|---|---|---|

| MPU | 1 | zmienny | procesor | ||

| A | Blichtr | 4 | zmienny | Agnus (wewnętrzny) | daje 1/4 cykli do procesora, gdy BLTPRI nie jest aktywny |

| B | Bitplan | 6 | 80 | Denise | osłabia kanały duszków przy poważnym overscan |

| C | Miedź | 1 | zmienny | Agnus (wewnętrzny) | |

| D | Audio | 4 | 4 | Paula | |

| mi | Sprite'y | 8 | 16 | Denise | |

| F | Dysk | 1 | 3 | Paula | |

| G | Odświeżanie pamięci | 1 | 4 | - | |

| Odniesienie: Instrukcja serwisowa Amigi 500 plus | |||||

Pinout

Wersje PLCC

Podczas wymiany lub modernizacji układów scalonych należy zadbać o układ pinów. Typy są wymienione tylko w celach informacyjnych; czterocyfrowe typy i styki / użycie nie są spójne.

| Szpilka | OC/ECS | ECS | AGA (Alicja) | Opis | |

|---|---|---|---|---|---|

| A500/2000 | A3000 | A500+/600 | A4000/1200 | ||

| 8370/1 | 8372 | 8375 | 8374 | ||

| 1 | RD13 | DRD13 | DRD13 | DRD13 | Magistrala danych 16 bitów, bit 13 |

| 2 | RD12 | DRD12 | DRD12 | DRD12 |

. . . |

| 3 | RD11 | DRD11 | DRD11 | DRD11 | |

| 4 | RD10 | DRD10 | DRD10 | DRD10 | |

| 5 | RD9 | DRD9 | DRD9 | DRD9 | |

| 6 | RD8 | DRD8 | DRD8 | DRD8 | |

| 7 | RD7 | DRD7 | DRD7 | DRD7 | |

| 8 | RD6 | DRD6 | DRD6 | DRD6 | |

| 9 | RD5 | DRD5 | DRD5 | DRD5 | |

| 10 | RD4 | DRD4 | DRD4 | DRD4 | |

| 11 | RD3 | DRD3 | DRD3 | DRD3 | |

| 12 | RD2 | DRD2 | DRD2 | DRD2 | |

| 13 | RD1 | DRD1 | DRD1 | DRD1 | |

| 14 | RD0 | DRD0 | DRD0 | DRD0 | Magistrala danych 16 bitów, bit 0 |

| 15 | Vcc | Vcc | Vcc | Vcc1 | +5V ±5% |

| 16 | RST* | _RESETOWANIE | _RESETOWANIE | /RESETOWANIE | Globalny RESETn, niski aktywny |

| 17 | INT3 | _INTR | _INTR | /WETR | |

| 18 | DMAL | DMAL | DMAL | DMAL | |

| 19 | BLS* | _ROZKOSZ | _ROZKOSZ | /BLS | |

| 20 | DB* | _BLIT | _BLIT | /DBR | |

| 21 | RRW | _MY | _MY | /MY | |

| 22 | PRW | R/W | R/W | R/W | |

| 23 | RGEN* | _REGEN | _REGEN | _REGEN | |

| 24 | JAK* | _JAK | _JAK | NC2 | |

| 25 | RAMEN* | _RAMEN | _RAMEN | /RAMEN | |

| 26 | RGA8 | RGA8 | RGA8 | RGA8 | |

| 27 | RGA7 | RGA7 | RGA7 | RGA7 | |

| 28 | RGA6 | RGA6 | RGA6 | RGA6 | |

| 29 | RGA5 | RGA5 | RGA5 | RGA5 | |

| 30 | RGA4 | RGA4 | RGA4 | RGA4 | |

| 31 | RGA3 | RGA3 | RGA3 | RGA3 | |

| 32 | RGA2 | RGA2 | RGA2 | RGA2 | |

| 33 | RGA1 | RGA1 | RGA1 | RGA1 | |

| 34 | 28MHz | 28MHz | 28MHz | SCLK | |

| 35 | XCLK | A20 | A20 | A20 | |

| 36 | XCLKEN* | _XCLKEN | _CDAC | 14MHz | |

| 37 | CDAC* | _CDAC | 7MHz | /CDAC | |

| 38 | 7MHz | 7MHz | CCKQ | 7MHz | |

| 39 | CCKQ | CCKQ | CCK | CCKQ | |

| 40 | CCK | CCK | 14 mln | CCK | |

| 41 | TEST | TEST | GND | /NTSC | |

| 42 | Vss | Vss1 | DRA0 | GND2 | |

| 43 | MA0 | DRA0 | DRA1 | DRA0 | Magistrala adresowa pamięci 9 bitów, bit 0 (z wyjątkiem 8375, który jest bitem 1) |

| 44 | MA1 | DRA1 | DRA2 | DRA1 |

. . . |

| 45 | MA2 | DRA2 | DRA3 | DRA2 | |

| 46 | MA3 | DRA3 | DRA4 | DRA3 | |

| 47 | MA4 | DRA4 | DRA5 | DRA4 | |

| 48 | MA5 | DRA5 | DRA6 | DRA5 | |

| 49 | MA6 | DRA6 | DRA7 | DRA6 | |

| 50 | MA7 | DRA7 | DRA8 | DRA7 | |

| 51 | MA8 | DRA8 | _LDS | DRA8 | Magistrala adresowa pamięci 9 bitów, bit 8 (z wyjątkiem 8375, który jest bitem _LDS) |

| 52 | SLD* | _LDS | _UDS | Vcc2 | |

| 53 | UDS* | _UDS | _CASL | NC1 | |

| 54 | CASL* | _CASL | _CASU | /CAS | |

| 55 | CASU* | _CASU | DRA9 | Vbb | |

| 56 | RAS1* | DRA9 | _RAS1 | DRA9 | |

| 57 | RAS0* | _RAS | _RAS0 | /RAS | |

| 58 | Vss | Vss2 | GND | GND3 | |

| 59 | A19 | A19 | A19 | A19 | |

| 60 | A1 | A1 | A1 | A1 | |

| 61 | A2 | A2 | A2 | A2 | |

| 62 | A3 | A3 | A3 | A3 | |

| 63 | A4 | A4 | A4 | A4 | |

| 64 | A5 | A5 | A5 | A5 | |

| 65 | A6 | A6 | A6 | A6 | |

| 66 | A7 | A7 | A7 | A7 | |

| 67 | A8 | A8 | A8 | A8 | |

| 68 | A9 | A9 | A9 | A9 | |

| 69 | A10 | A10 | A10 | A10 | |

| 70 | A11 | A11 | A11 | A11 | |

| 71 | A12 | A12 | A12 | A12 | |

| 72 | A13 | A13 | A13 | A13 | |

| 73 | A14 | A14 | A14 | A14 | |

| 74 | A15 | A15 | A15 | A15 | |

| 75 | A16 | A16 | A16 | A16 | |

| 76 | A17 | A17 | A17 | A17 | |

| 77 | A18 | A18 | A18 | A18 | |

| 78 | LP* | _LPEN | _LPEN | /LPEN | |

| 79 | VSY* | _SYNC | _SYNC | /VSYNC | |

| 80 | CSY* | _CSYNC | _CSYNC | /CSYNC | |

| 81 | HSY* | _HSYNCH | _HSYNCH | /HSYN | |

| 82 | Vss | Vss3 | GND | GND1 | Masa, wspólna na całej płycie |

| 83 | RD15 | DRD15 | DRD15 | DRD15 | Magistrala danych 16 bitów, bit 15 |

| 84 | RD14 | DRD14 | DRD14 | DRD14 | Magistrala danych 16 bitów, bit 14 |

Materiały referencyjne: szkolenie serwisowe A500, instrukcja serwisowa A3000, instrukcja serwisowa A500+, schematy A1200

Zobacz też

- Źródła

- AMIGA 1000 NAPRAWA POZIOMU MONTAŻU (Commodore-Amiga, Inc.) 1985 PN 314038-01 Dave's Amiga Schematics and Manuals

- Commodore Amiga A500/A2000 Technical Reference Manual (Commodore-Amiga, Inc.) 1987 Dave's Amiga Schematics and Manuals

- A500 SYSTEM SCHEMATICS LISTA CZĘŚCI KOMPONENTÓW (Rev 6A/7) Dave's Amiga Schematics and Manuals

- SCHEMATY SYSTEMU A3000 (Commodore Business Machines, Inc.) Marzec 1990 PN-314677-01 www.1000bit.net

- CDTV SERVICE MANUAL (Commodore International Spare GmbH) Maj 1991 PN-400403-01 www.ianstedman.co.uk (plik ZIP)

- A500 PLUS INSTRUKCJA SERWISOWA (Commodore International Spare GmbH) Październik 1991 PN-400420-01 www.1000bit.net

- SCHEMATIC SYSTEMU A600 (Commodore International Spare GmbH) kwiecień 1992 PN-400422-02 www.1000bit.net

- ZOBOWIĄZANIE: les chipsets de l'Amiga

- Wielka księga sprzętu Amigi

- alexh na angielskiej płycie Amigi (informacje o Agnus 8372B)

- National Amiga Inc. odzwierciedlenie na l8r.net

- Sprzedawane modele Commodore Amiga

- AMIGA Auckland Inc.

- Uniwersytet Amigi

- Internetowe muzeum komputerów Commodore

- Notatki