Sygnatura 8X300

| Informacje ogólne | |

|---|---|

| Wystrzelony | 1976 |

| Zaprojektowany przez | Mikrosystemy naukowe (SMS) |

| Wspólni producenci |

|

| Wydajność | |

| Maks. Częstotliwość taktowania procesora | do 8MHz |

| Szerokość danych | 16 instrukcji, 8 danych |

| Szerokość adresu | 13 instrukcji, 1 dane |

| Architektura i klasyfikacja | |

| Instrukcje | 8 |

| Specyfikacje fizyczne | |

| pakiet(y) |

|

| Historia | |

| Następca | 8X305 |

8X300 to mikroprocesor produkowany i sprzedawany przez Signetics od 1976 roku jako drugie źródło SMS 300 przez Scientific Micro Systems, Inc. Chociaż SMS opracował SMS 300, Signetics był jedynym producentem tej linii produktów. W 1978 Signetics nabył prawa do serii SMS 300 i przemianował ją na 8X300.

Został zaprojektowany jako szybki mikrokontroler i procesor sygnałowy iz tego powodu znacznie różni się od konwencjonalnych mikroprocesorów logicznych NMOS tamtych czasów. Być może główną różnicą było to, że został zaimplementowany w technologii bipolarnego tranzystora Schottky'ego i mógł pobierać, dekodować i wykonywać instrukcje w zaledwie 250 ns. Dane mogą być wprowadzane z jednego urządzenia, modyfikowane i wysyłane do innego urządzenia podczas jednego cyklu instrukcji.

W 1982 roku firma Signetics wypuściła ulepszoną i szybszą wersję, 8X305. Procesor ten stał się bardzo popularny w zastosowaniach wojskowych i był drugim źródłem firmy Advanced Micro Devices jako AM29X305. Ostatecznie prawa do produkcji zostały sprzedane firmie Lansdale Semiconductor Inc., która od 2017 r. Nadal oferowała 8X305. Klon 8X300 został wyprodukowany w Związku Radzieckim pod oznaczeniem KM1818VM01 ( rosyjski : КМ1818ВМ01 ).

Architektura

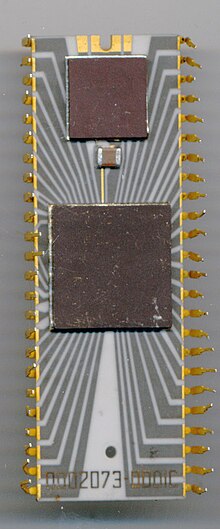

Urządzenie zostało dostarczone w 50-pinowej obudowie ceramicznej DIL i jest zasilane z pojedynczej szyny zasilającej 5V. Do uzupełnienia wbudowanego w układ regulatora napięcia, który dostarcza napięcie 3 V do wybranych obszarów układu scalonego, wymagany jest zewnętrzny tranzystor przepustowy. Pomaga to ograniczyć całkowity pobór prądu do mniej niż 450 mA.

Wymagania dotyczące zegara są spełnione poprzez podłączenie kryształu 8 MHz bezpośrednio do dwóch pinów. Alternatywnie można użyć sygnałów pozafazowych z zewnętrznego generatora zegara.

Drugą unikalną cechą jest dedykowany 13-bitowy adres i 16-bitowa magistrala danych umożliwiająca dostęp do pamięci programu, umożliwiając bezpośrednie adresowanie 8192 16-bitowych słów programu. Pozwala to na bezpośrednie podłączenie pamięci programów ROM / PROM bez dodatkowego sprzętu. Druga połączona 8-bitowa magistrala adresu/danych, magistrala wektora interfejsu (IV), jest używana do danych i we/wy. Dwa sygnały sterujące, WC (polecenie zapisu) i SC (polecenie wyboru), określają stan szyny IV w następujący sposób:

- SC=1, WC=0: Adres I/O jest wysyłany na szynę IV

- SC=0, WC=1: Dane I/O są wyprowadzane na magistralę IV

- SC=0, WC=0: Oczekiwane są dane wejściowe I/O na szynie IV

Kolejne dwa sygnały, LB (wybór lewego banku) i RB (wybór prawego brzegu), skutecznie podwajają przestrzeń adresową magistrali IV i były najczęściej używane do przełączania między pamięcią RAM w jednym banku a portami we / wy w drugim.

Inną niezwykłą cechą jest to, że zamiast wykonywać instrukcje maskowania, obracania, przesuwania i scalania w jednostce arytmetycznej (ALU), jak ma to miejsce w przypadku większości mikroprocesorów, 8X300 ma oddzielne jednostki maskowania, obracania, przesuwania i scalania. Dane można zatem obracać, maskować, modyfikować, przesuwać i łączyć (w tej kolejności), a wszystko to w jednym cyklu instrukcji.

Zestaw instrukcji

Procesor zwykle przetwarza 8-bitowe bajty danych, ale jednostka maskująca umożliwia manipulowanie jednym lub wieloma bitami, co czyni go procesorem o zmiennej długości danych. Dane wewnętrzne są przechowywane w 8-bitowych rejestrach do odczytu/zapisu — od R1 do R6, R9 oraz w rejestrze pomocniczym (R0). Rejestr pomocniczy zawiera jeden z argumentów używanych w instrukcjach dwuargumentowych, takich jak ADD lub AND, a jednobitowy (tylko do odczytu) rejestr przepełnienia (R8) przechowuje bit przeniesienia z operacji ADD. Dwa wirtualne rejestry tylko do zapisu IVL (R7) i IVR (R15) służą do umieszczania adresu na szynie IV, a dwa zestawy ośmiu rejestrów wirtualnych (R16-R23 i R24-R31) służą do przesyłania danych do lub z szyny IV. W tym drugim przypadku dwa górne bity numeru rejestru wybierają lewy lub prawy bank, a trzy dolne bity określają liczbę miejsc, o które dane mają zostać obrócone. 8-bitowy bufor szyny IV przechowuje kopię ostatnich danych, które mają być przesłane do lub z szyny IV. Te dane są używane w operacjach scalania.

Trzy najbardziej znaczące bity instrukcji definiują opcode i dzielą instrukcje na osiem klas:

- Instrukcja MOVE umożliwia skopiowanie zawartości wybranych rejestrów, umieszczenie na szynie IV, odczytanie z szyny IV lub przeniesienie z szyny IV na szynę IV.

- Klasy ADD, AND i XOR są podobne, z tą różnicą, że w tych instrukcjach zawartość rejestru pomocniczego jest łączona z rejestrem źródłowym przed wykonaniem części MOVE instrukcji.

- Instrukcja XEC umożliwia wykonanie wybranej instrukcji pod innym adresem lokalnym i innym przesunięciem bez zwiększania licznika programu.

- Instrukcja NZT pozwala na zaimplementowanie rozgałęzienia warunkowego.

- Instrukcja XMIT umożliwia umieszczenie określonego w instrukcji 8-bitowego wzorca binarnego w określonym rejestrze lub na szynie IV. Jest to podobne do instrukcji ładowania natychmiastowego.

- Instrukcja JMP wykonuje bezwarunkowe rozgałęzienie do dowolnego miejsca w pamięci programu zawierającego 8192 słów.

Użycie pozostałych 13 bitów instrukcji zależy od kodu operacyjnego:

- Instrukcje MOVE, AND, ADD i XOR: 5 bitów służy do zdefiniowania rejestru źródłowego, 3 bity służą do zdefiniowania dowolnej operacji obracania lub maskowania (pole R/L), a pozostałe 5 bitów określa rejestr docelowy.

- XEC i NZT: 5 bitów służy do zdefiniowania rejestru źródłowego, pozostałe 8 bitów określa pole adresowe.

- XEC: zawartość rejestru źródłowego jest najpierw dodawana do pola adresu, które jest następnie używane jako 8 niższych bitów adresu programu.

- NZT: skok jest wykonywany, jeśli rejestr źródłowy jest niezerowy. Jeśli skok jest wykonywany, pole adresowe jest używane jako 8 niższych bitów adresu programu.

- XMIT: 5 bitów służy do zdefiniowania rejestru docelowego, pozostałe 8 bitów określa dane.

- JMP: wszystkie 13 bitów jest używane jako adres bezwzględny w pamięci programu.

Przesuwaj, obracaj, maskuj i łącz

Jednostki obracania i maskowania znajdują się między bankiem rejestrów a jednostką ALU. Dlatego wszystkie dane można w zasadzie obrócić i zamaskować, zanim trafią do jednostki ALU.

- Rotate Unit: To urządzenie obróci dane w PRAWO o liczbę miejsc określoną w kodzie operacyjnym.

- Jednostka maski: Ta jednostka zamaskuje (ustawi na zero) górne bity danych, aby zachować liczbę dolnych bitów określoną w kodzie operacyjnym.

Jednostki Shift i Merge znajdują się pomiędzy ALU a szyną IV, dzięki czemu wszelkie dane przesyłane do szyny IV mogą zostać przesunięte i scalone przed wysłaniem.

- Shift Unit: Ta jednostka przesunie dane w LEWO o liczbę miejsc określoną w kodzie operacyjnym.

- Jednostka scalania: Ta jednostka scala (zastępuje) liczbę bitów określoną przez kod operacji w buforze magistrali IV z danymi przed umieszczeniem zawartości bufora na szynie IV.

Uwaga: zliczenie zerowej liczby bitów do scalenia spowoduje zastąpienie wszystkich 8 bitów.

W zależności od źródła i miejsca docelowego możliwe są następujące kombinacje:

- Instrukcje MOVE, ADD, AND i XOR:

- rejestr do rejestru (w tym rejestry IVL i IVR): Obróć

- zarejestruj się na magistrali IV (wyjście danych): przesuń i połącz

- Wejście IV-bus do rejestracji: obracanie i maskowanie

- Wejście IV-bus do wyjścia IV-bus: obracanie, maskowanie, przesuwanie i łączenie

- Wejście IV-bus do rejestru IVL lub IVR (wyjście adresu IV-bus): obracanie i maskowanie

- XEC i NZT:

- wejście IV-bus: obracanie i maskowanie

- XMIT

- IV-bus: przesunięcie i połączenie

we/wy

Przesyłanie danych do iz 8X300 to proces dwuetapowy:

- Krok 1: Wykorzystując jedną z instrukcji MOVE, ADD, AND, XOR lub XMT i określając jeden z rejestrów wirtualnych IVL (lewy brzeg) lub IVR (prawy brzeg) jako miejsce docelowe, adres jest wyprowadzany na szynę IV wraz z Wybierz sygnały Command i Bank Select.

Ponieważ adres we/wy jest wyprowadzany oddzielnie, porty we/wy muszą utrzymywać (zatrzaskiwać) wybór. Można to zrobić za pomocą oddzielnych dekoderów i zatrzasków adresu lub portu I/O ze zintegrowanym dekodowaniem i zatrzaskiem adresu, takiego jak 8X32. Ze względu na zatrzaskiwanie, raz zaadresowane porty we/wy pozostają aktywne do momentu wyprowadzenia innego adresu i można uzyskać do nich dostęp wielokrotnie bez konieczności ponownego adresowania. Dwa porty I/O (lub adresy RAM) mogą być aktywne w tym samym czasie, wykorzystując sygnały Bank Select do szybkiego przełączania między nimi bez dalszego adresowania.

- Krok 2: Dane są przesyłane do lub z 8X300 przy użyciu jednej z instrukcji MOVE, ADD, AND lub XOR i określając jeden z rejestrów R16-R31 jako źródło i/lub miejsce docelowe. Wybrany rejestr określa, który sygnał Bank Select towarzyszy przelewowi.

Aplikacje

W obszernej nocie aplikacyjnej firma Signetics pokazała, jak wykorzystać 8X300 jako kontroler dyskietek . Poprawiona nota aplikacyjna wykazała użycie 8X300 razem z 8X330. Inne opisane uwagi aplikacyjne:

- Teleskopowy multiplekser _

- Koncentrator danych

- Zdalny kontroler terminala

- Emulator magistrali we/wy komputera

- Interfejs pamięci RAM

System demonstracyjny (zawarty w teczce) i notatka aplikacyjna pokazały, że 8X300 jest używany w kontrolerze sygnalizacji świetlnej.

Olivetti użył 8X300, a później 8X305 jako kontrolera dysku twardego ST506 z serii komputerów osobistych M20 .

Convergent Technologies użył 8X300, 8X320 i 8X330 w swoim kontrolerze dysku twardego AWS w 1981 roku.

Western Digital użył 8X300 w swoim kontrolerze dysku twardego WD1000 ST506 i 8X305 w swoim kontrolerze dysku twardego WD1001 ECC.

Urządzenia pomocnicze

- 8X01: Cykliczny kontroler nadmiarowości

- 8X31 / 8T31: 8-bitowy dwukierunkowy port we/wy z zatrzaskiem

- 8X32 / 8X36 / 8X42: 8-bitowy zatrzaskowy adresowalny dwukierunkowy port we/wy

- 8T39: Adresowalny ekspander magistrali

- 8X41: Asynchroniczny dwukierunkowy przedłużacz i repeater magistrali (SABRE)

- 8T58: Przezroczysty ekspander magistrali

- 8X320: Tablica rejestrów interfejsu magistrali

- 8X330: Formater/kontroler dyskietek

- 8X350: 2048-bitowa dwubiegunowa pamięć RAM (256*8) 35 ns czas dostępu

- SMS360 / 8X360: Bajt wektora interfejsu