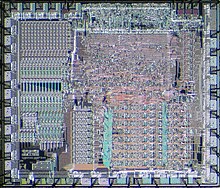

Sygnety 2650

Signetics 2650AN

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | 1975 |

| Wspólni producenci | |

| Wydajność | |

| Maks. Częstotliwość taktowania procesora | 1,2 MHz |

| Szerokość danych | 8 |

| Szerokość adresu | 15 |

| Specyfikacje fizyczne | |

| pakiet(y) |

|

Signetics 2650 był 8-bitowym mikroprocesorem wprowadzonym na rynek w lipcu 1975 roku. Według książki Adama Osborne'a An Introduction to Microprocessors Vol 2: Some Real Products , był to „najbardziej podobny do minikomputera ” z dostępnych wówczas mikroprocesorów. Połączenie brakujących funkcji i dziwnego dostępu do pamięci ograniczyło jego atrakcyjność, a system nie był używany na rynku.

Rozwój

W 1972 roku Jack Curtis z Signetics zatrudnił Johna Kesslera z IBM do kierowania projektem nowego jednoukładowego procesora, który miał konkurować z systemami minikomputerów . Kessler wybrał IBM 1130 jako model dla nowego projektu. 1130, wydany w 1965 roku, był 16-bitowym minikomputerem , który miał wiele wspólnych cech konstrukcyjnych z innymi minikomputerami z tamtej epoki.

Podczas gdy Kessler projektował architekturę, Kent Andreas rozplanował procesor przy użyciu niedawno opracowanego procesu implantacji jonów NMOS . W przeciwieństwie do znacznie bardziej powszechnego PMOS tamtej epoki, NMOS zużywał mniej energii i rozpraszał mniej ciepła. Pozwoliło to na pracę chipa z wyższymi prędkościami niż projekty procesorów PMOS, a pierwsze 2650 działały z tą samą prędkością 1,25 MHz, co współczesne modele 1130.

Kiedy został zaprojektowany w 1972 roku, 2650 był jednym z najbardziej zaawansowanych projektów na rynku, z łatwością przewyższając pod względem wydajności i funkcji Intel 4004 i 8008 z tej samej epoki. Mimo to projekt nie został dopuszczony do produkcji. W tym czasie firma Signetics była mocno zaangażowana w Dolby Laboratories , opracowując układy scalone , które implementowały zestaw systemów redukcji szumów Dolby . Produkcja 2650 została cofnięta, a procesor został formalnie wprowadzony dopiero w lipcu 1975 r. Do 1975 r. Wprowadzono kilka nowych procesorów, zaprojektowanych od początku jako maszyny 8-bitowe, a nie naśladujące starszą konstrukcję, a zalety 2650 nie były już tak przekonujące.

W 1975 roku Philips kupił Signetics i od tego momentu wersje 2650 można znaleźć zarówno z marką Signetics, jak i Philips.

W marcu 1976 roku Signetics zawarł umowę drugiego źródła z Advanced Memory Systems (AMS). W tamtym czasie większość firm zajmujących się procesorami była bardzo mała i nikt nie kupiłby projektu od firmy, która mogłaby zbankrutować. Drugie źródło zaopatrzenia było ważną gwarancją, że projekt pozostanie dostępny w tej ewentualności. AMS działał już jako drugie źródło dla RCA 1802 , zaawansowanej konstrukcji CMOS , a NMOS 2650 był postrzegany jako użyteczny dodatek, który nie będzie bezpośrednio konkurował z 1802. Niestety, w listopadzie AMS został zakupiony przez Intersil , który własny Intersil 6100 , jednoukładowa wersja PDP-8 mini. Intersil zrezygnował z produkcji 2650.

Signetics spróbował ponownie z National Semiconductor w 1977 roku, który planował wprowadzenie wersji w ostatnim kwartale roku. Wydaje się, że z nieznanych powodów nigdy to się nie wydarzyło i znaleziono tylko jeden egzemplarz wersji NS z Francji.

Signetics kontynuował rozwój 2650, wprowadzając dwa nowe modele w 1977 roku. 2650A był przerobioną wersją oryginalnego układu, mającą na celu poprawę wydajności, a tym samym obniżenie kosztów. Szybkość pozostała niezmieniona i wynosiła 1,25 MHz dla modelu podstawowego i 2 MHz dla wersji -1. 2650B był oparty na A, dodał szereg nowych instrukcji i poprawił wydajność wielu istniejących instrukcji.

Opis

| 1 4 | 1 3 | 1 2 | 1 1 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | (pozycja bitu) |

|

Alternatywne rejestry ogólnego przeznaczenia |

|||||||||||||||

| REG3' | |||||||||||||||

| REG2' | |||||||||||||||

| REG1' | |||||||||||||||

|

Główne rejestry ogólnego przeznaczenia |

|||||||||||||||

| REG3 | |||||||||||||||

| REG2 | |||||||||||||||

| REG1 | |||||||||||||||

| REG0 | |||||||||||||||

|

Instrukcja Rejestr adresowy |

|||||||||||||||

| Strona | |||||||||||||||

|

Stos adresów zwrotnych podprogramu |

|||||||||||||||

| S0 | |||||||||||||||

| S1 | |||||||||||||||

| S2 | |||||||||||||||

| S2 | |||||||||||||||

| S4 | |||||||||||||||

| S5 | |||||||||||||||

| S6 | |||||||||||||||

| S7 | |||||||||||||||

| Słowa stanu programu | |||||||||||||||

| S | F | II | Stos Ptr | zasilacz | |||||||||||

| CC | ID | RS | toaleta | OW | CM | C | PSL | ||||||||

Ogólny projekt 2650 został oparty na IBM 1130 . W związku z tym 2650 ma wiele funkcji, które były powszechne w minikomputerach z lat 60. , ale rzadko można je było znaleźć w nowo zaprojektowanych mikroprocesorach z lat 70. Wśród nich były na przykład bity stanu, które były używane do śledzenia stanu wejścia/wyjścia , co ułatwia pisanie kodu interfejsu. Inną mini-podobną funkcją było użycie przerwań wektorowych , które umożliwiały urządzeniom wywoływanie właściwej obsługi przerwań kod, umieszczając jego lokalizację w pamięci na szynie danych, a następnie wymuszając przerwanie. Pozwala to uniknąć konieczności pisania scentralizowanej obsługi przerwań, która odczytuje dodatkowe dane z magistrali, określa, który sterownik urządzenia jest wywoływany, a następnie wywołuje go; 2650 może przejść bezpośrednio do właściwego kodu, potencjalnie zapisanego w samym urządzeniu.

rejestry procesora 2650 zostały podzielone na zestawy, z pojedynczym rejestrem globalnym R0 używanym jako akumulator i dwoma zestawami trzech rejestrów indeksowych , oba nazwane R1, R2 i R3, w sumie siedem rejestrów. W dowolnym momencie jeden z dwóch zestawów indeksów był widoczny dla procesora. To, który zestaw był widoczny, było kontrolowane przez bit w rejestrze statusu PSW. Można było łatwo przełączać się między dwoma zestawami rejestrów za pomocą jednej instrukcji. Umożliwiło to szybkie przełączanie wartości podczas wywołań podprogramów systemu operacyjnego przełączników lub obsługi przerwań. W przeciwieństwie do 1130, rejestry miały tylko 8-bitową szerokość, a nie 16-bitową, aw 1130 były tylko dwa zestawy zamiast trzech.

Inną z jego mini-podobnych funkcji była rozbudowana obsługa adresowania pośredniego w większości instrukcji. Wiele instrukcji wymaga odczytania danych z lokalizacji w pamięci, w większości procesorów tamtej epoki byłby to pojedynczy bajt danych przechowywanych w pamięci, do której odnosi się 16-bitowa lokalizacja. W 2650 wysoki bit tej 16-bitowej lokalizacji wskazywał kierunek, co oznacza, że dane nie znajdowały się w tej lokalizacji w pamięci, ale w tej zakodowanej w pozostałych 15 bitach adresu. Ten styl dostępu umożliwiał łatwiejszy dostęp do bloków danych niż w systemach, które zapewniały pośrednictwo wyłącznie za pomocą specjalnych instrukcji lub wyłącznie za pośrednictwem rejestrów indeksowych. Można przejść przez pamięć, zwiększając wartość adresu przechowywaną w pamięci. Spowodowało to również zastosowanie znacznej liczby instrukcji matematycznych do adresów, a aby poprawić wydajność tych operacji, model 2650 zawierał drugi arytmetyczna jednostka logiczna tylko do obliczeń adresu.

Wadą tego podejścia było to, że wysoki bit nie był już częścią adresu, co oznaczało, że przestrzeń adresowa wynosiła tylko 15 bitów, a maszyna mogła uzyskać dostęp tylko do łącznie 32 KB pamięci. Przestrzeń adresowa została dodatkowo ograniczona przez użycie kolejnych dwóch bitów adresu do wskazania trybu indeksowania dla wszystkich instrukcji logicznych i arytmetycznych (tj. nierozgałęziających). Te bity kontrolują funkcje, takie jak to, czy adres powinien być post-inkrementowany, czy pre-dekrementowany, co jest niezwykle przydatne do konstruowania pętli. Ale biorąc pod uwagę wszystkie te bity, tylko 13 było dostępnych dla adresów w tych instrukcjach, co oznacza, że tylko 8 KB można było zaadresować bezpośrednio. Oznaczało to, że pamięć główna została podzielona na cztery bloki po 8 KB. Aby uzyskać dostęp do pamięci poza obszarem 8 KB, w którym znajdowała się instrukcja, wskazywane bajty danych musiały zawierać adres pośredni, wskazujący na inną lokalizację w pamięci. Wymusiło to kolejny cykl odczytu pamięci, spowalniając wydajność.

Kiedy 2650 został zaprojektowany w 1972 roku, te ograniczenia przestrzeni adresowej nie były znaczące ze względu na mały rozmiar i wysoki koszt statycznej pamięci RAM , zwykle używanej z tymi procesorami. W tamtym czasie maszyny zawierały zwykle 2 lub 4 KB pamięci RAM. Jednak wraz z rosnącym wykorzystaniem dynamicznej pamięci RAM od połowy lat 70. maszyny z 8 i 16 KB pamięci RAM, a ostatecznie 64 KB, stały się powszechne, a system adresowania w 2650 stał się znaczącą przeszkodą.

2650 zawierał również stos wywołań on-die , zamiast bardziej powszechnego rozwiązania, które rezerwuje miejsce w pamięci do przechowywania stosu. Wskaźnik stosu był przechowywany w trzech bitach w PSW. Stos na matrycy jest znacznie szybszy, ponieważ dostęp do danych można uzyskać bezpośrednio, bez czekania na odczytanie ich z pamięci zewnętrznej, ale zajmuje również miejsce na matrycy i zawsze ma ograniczony rozmiar w wyniku praktycznych kompromisów. W 2650 stos miał głębokość ośmiu 15-bitowych wpisów, co jest generalnie o wiele za małe, aby można go było używać w językach wysokiego poziomu .

Chociaż istniało dziewięć różnych trybów adresowania , brak 16-bitowych rejestrów i 13-15-bitowej przestrzeni adresowej uniemożliwił powszechne użycie. Mimo to system operacyjny („2650 DOS”) wraz z interpreterami BASIC 8 KB i 12 KB (sprzedawanymi przez Central Data Corporation USA) oraz wieloma grami w stylu Hunt the Wumpus . Większość programów została napisana w asemblerze .

Używa

mikroprocesorowe płytki rozwojowe oparte na 2650 , najpierw PC1001, a następnie jego następcę, „Adaptable Board Computer” PC1500, w cenie od 165 do 400 AUD. Sam chip sprzedawano za około 20 dolarów australijskich. Kilka projektów budowy sprzętu i artykułów programistycznych zostało opublikowanych w magazynach takich jak Electronics Australia i Elektor , a powiązane zestawy były sprzedawane w sklepach elektronicznych. Czynniki te doprowadziły do jego wykorzystania przez wielu hobbystów w wielu krajach, takich jak Australia, USA, Wielka Brytania, Holandia i Niemcy.

Signetics 2650 lub 2650A wykorzystywały dwa typy konsoli do gier wideo . Pierwsza grupa konsol bazuje na kontrolerze wyświetlacza wideo Signetics 2636 ; do tej grupy należy 1292 Advanced Programmable Video System i blisko spokrewniony Interton Video Computer 4000 . Zostały one wydane w Niemczech odpowiednio w 1976 i 1978 roku. Druga grupa konsol była oparta na Signetics 2637 jako kontrolerze wyświetlania wideo ; Emerson Arcadia 2001 , który został wydany w 1982 roku i który wykorzystywał Signetics 2650 działający na 3,58 MHz jako procesor należą do tej grupy wraz z wieloma innymi kompatybilnymi programowo (Leonardo, Hanimex MPT-03 itp.).

W latach 70. wydano co najmniej sześć gier wideo na monety, które korzystały z procesora 2650: Atari, Inc. Quiz Show , Meadows Games 3D Bowling , Meadows Games Gypsy Juggler , Meadows Games Lazer Command , Cinematronics Embargo i klon Space z 1978 roku Invaders autorstwa Zaccaria o nazwie The Invaders (oryginał autorstwa Taito wykorzystuje procesor Intel 8080 ).

Włoski producent gier Zaccaria wypuścił 28 automatów do gry w pinball opartych na procesorze 2650. Ich następca, MrGame, wypuścił cztery dodatkowe automaty do gry w jednoręki bandyta używając 2650. Zaccaria udzielił licencji na swój projekt również firmie Technoplay, a kilka innych automatów do gry w jednoręki bandyta zostało wydanych przy użyciu odmian projektów płytek drukowanych Zaccaria .

Co najmniej dwie gry wideo na monety zostały wydane w latach 80. przy użyciu 2650. Hunchback i Hunchback Olympic.

Procesor był również używany w Signetics Instructor 50, który był małym komputerem przeznaczonym do nauki obsługi i programowania procesora Signetics 2650.

Model 2650 był również używany w niektórych dużych elementach wyposażenia, takich jak Tektronix 8540, system opracowywania oprogramowania mikroprocesorowego, który obsługiwał różne emulatory w obwodzie , karty pamięci śledzenia i analizatory stanów logicznych do debugowania systemów mikroprocesorowych w czasie rzeczywistym, zgodnie z praktyką w latach 80. . Model 2650 zapewniał podstawowe funkcje systemu operacyjnego, przesyłanie danych i interfejs do komputera głównego lub szeregowego terminala komputerowego.

Procesor najlepiej nadawał się jako mikrokontroler ze względu na rozbudowaną obsługę wejść/wyjść:

- Jednobitowe piny wejścia/wyjścia na procesorze (bity wykrywania/flagi)

- Sygnały adresowane bezpośrednio do dwóch 8-bitowych portów we/wy (porty sterujące i porty danych) przy użyciu instrukcji jednobajtowych ( port we/wy ). W ten sposób ominięto skomplikowany sprzęt, potrzebny innym systemom do operacji we/wy mapowanych w pamięci

- Sygnały do adresowania kolejnych 256 portów we/wy przy użyciu adresu 8-bitowego i instrukcji dwubajtowych, ponownie ograniczając ilość wymaganego sprzętu (dekodowanie adresu). Firma Philips podkreśliła to zastosowanie jako mikrokontrolera w programie demonstracyjnym pokazującym, że 2650 steruje inteligentnym systemem windy. Ponadto na targach pokazywali model 2650 kontrolujący miniaturowego robota sortującego i układającego

Przemysłowy System Mikrokomputerowy – IMS

Przez krótki czas, począwszy od 1979 roku, Philips sprzedawał modułowy komputer 2650 o nazwie „IMS” – Industrial Microcomputer System, oparty na formacie Eurocard w 19-calowej szafie typu rack. Zawierał moduły CPU , PROM, RAM , wejścia, wyjścia i teletype. To system miał być bardziej inteligentnym programowalnym sterownikiem logicznym.Na potrzeby rozwoju dodano później moduły DEBUG, DISPLAY, INTERRUPT i MODEST (programator (E)PROM).

Architektura

Model 2650 był dostarczany w 40-pinowej plastikowej lub ceramicznej obudowie DIL . Potrzebny był zewnętrzny jednofazowy sygnał zegarowy i pojedyncze zasilanie 5V.

2650 miał wiele niezwykłych cech w porównaniu z innymi mikroprocesorami tamtych czasów:

- Był to w pełni statyczny 8-bitowy mikroprocesor NMOS. Statyczny charakter był niezwykły jak na tamte czasy i oznaczał, że procesor można było zatrzymać po prostu przez zatrzymanie sygnału zegara. Programiści z wdzięcznością wykorzystali tę funkcję do „pojedynczego kroku” w programie za pomocą przełącznika przyciskowego do generowania impulsów zegara.

- Unikalny był 8-poziomowy 15-bitowy szeroki stos dla adresów zwrotnych podprogramów i przerwań, który został zintegrowany z procesorem. Wskaźnik stosu wykorzystywał 3 bity górnego rejestru stanu. Oznaczało to, że podprogramy i przerwania mogły być zagnieżdżane tylko do 8 poziomów.

- Procesor miał tylko 13 rzeczywistych linii adresowych, kolejne 2 linie adresowe były podłączone do 2-bitowego „rejestru strony”, co dało przestrzeń adresową 32 KB. Rejestr strony był ustawiany, gdy wykonywana była bezwzględna (bezpośrednia) instrukcja rozgałęzienia, która wykorzystywała pełny adres 15-bitowy. Wszystkie instrukcje logiczne i arytmetyczne wykorzystywały 13-bitowy adres powiększony o zawartość rejestru strony, ograniczając w ten sposób ich zakres do strony o rozmiarze 8 KB. Te 2 górne linie adresowe były również używane (multipleksowane) do wyboru odpowiedniego portu I/O podczas operacji I/O (port kontrolny, port danych lub port rozszerzony).

- Chociaż 2650 miał tylko jedno wejście przerwania, było to przerwanie „wektorowe” - urządzenie przerywające musiało umieścić przesunięcie względem zera na szynie danych, które byłoby używane jako operand ZBSR (gałąź zerowa do względnego podprogramu) instrukcja rozgałęzienia do określonej procedury przerwania. Dlatego przy użyciu adresowania pośredniego w pierwszych 64 bajtach pamięci można było zapisać maksymalnie 30 wektorów przerwań. (Pierwsze trzy bajty były potrzebne do utrzymania bezwarunkowego rozgałęzienia procedury „resetowania”). To przerwanie wektorowe również przypomina minikomputer PDP-11 .

Zestaw instrukcji

Chociaż 2650 jest w zasadzie 8-bitowym mikroprocesorem, 64 kody operacji są w rzeczywistości 9-bitowe, a kolejne 32 kody operacyjne są 11-bitowe (wykorzystujące bity w polu adresu). Z pozostałych 128 8-bitowych kodów operacji zaimplementowano 124 (126 w 2650B), co daje łącznie 444 (446) instrukcji.

Dostępnych jest znacznie więcej instrukcji, ponieważ zachowanie standardowych instrukcji można modyfikować, ustawiając lub usuwając bity stanu: WC (z przeniesieniem lub bez) i COM (porównanie logiczne lub arytmetyczne). To podwoiło liczbę instrukcji obracania, dodawania, odejmowania i porównywania.

Zestaw instrukcji jest silnie ortogonalny : wszystkie instrukcje logiczne i arytmetyczne mogą wykorzystywać wszystkie dziewięć trybów adresowania:

- rejestr

- natychmiastowy

- PC względny i PC względny pośredni

- bezwzględny i bezwzględnie pośredni

- indeksowane bezwzględnie, indeksowane bezwzględnie z automatycznym przyrostem i indeksowane bezwzględnie z automatycznym zmniejszaniem, zarówno bezpośrednie, jak i pośrednie

Najbardziej znaczący bit wszystkich adresów względnych i bezwzględnych jest używany do wskazania kierunku .

Jedynymi wyjątkami są sytuacje, w których kody operacyjne bezsensownych operacji są używane do innych celów:

- kod operacji dla rejestru AND zero z rejestrem zero jest używany dla instrukcji HALT.

- kod operacji dla rejestru STORE zero w rejestrze zero jest używany dla instrukcji NOP .

Chociaż instrukcja LOAD rejestr zero z rejestrem zero wydawałaby się bez znaczenia i była oficjalnie nieobsługiwana, ustawiała kod warunku i była często używana do określenia statusu tego rejestru. [ potrzebne źródło ] . Signetics Assembler wygenerował kod tak, jakby to była instrukcja IORZ,R0.

Indeksowanie

We wszystkich instrukcjach arytmetycznych i logicznych wykorzystujących adresowanie bezwzględne (bezpośrednie), bity 14 i 13 pola adresowego są używane do wskazania trybu indeksowania w następujący sposób:

- 00 brak indeksowania

- 01 indeksowanie z automatycznym przyrostem

- 10 indeksowania z automatycznym zmniejszaniem

- 11 tylko indeksowanie

Gdy określono indeksowanie, rejestr zdefiniowany w instrukcji staje się rejestrem indeksu, a źródło/przeznaczenie jest niejawnie rejestrem zerowym. W przypadku indeksowania pośredniego stosuje się indeksowanie typu Post, tzn. adres pośredni jest najpierw pobierany z pamięci, a następnie dodawany jest do niej indeks.

Rozgałęzienie

Prawdopodobnie najbardziej minikomputerowym aspektem 2650 jest ogromna liczba (62) instrukcji rozgałęzień (skoków); wszystkie te instrukcje mogą również wykorzystywać pośredniość:

- BIRR i BIRA: Rejestr przyrostowy i rozgałęzienie, jeśli niezerowe (R0, R1, R2 lub R3) z adresowaniem względnym lub bezwzględnym

- BDRR i BDRA: Rejestr dekrementacji i rozgałęzienie, jeśli są niezerowe (R0, R1, R2 lub R3) z adresowaniem względnym lub bezwzględnym

- BRNR i BRNA: rozgałęzienie, jeśli rejestr jest niezerowy (R0, R1, R2 lub R3) z adresowaniem względnym lub bezwzględnym

- BCTR i BCTA: rozgałęzienie na warunku True (zero, większe niż, mniejsze niż lub bezwarunkowe) z adresowaniem względnym lub bezwzględnym

- BCFR i BCFA: rozgałęzienie na warunku Fałsz (zero, więcej niż lub mniej niż) z adresowaniem względnym lub bezwzględnym.

- ZBRR: gałąź względem adresu zero

- BXA: oddział indeksowany

Podobnie jak Intel 8080 , 2650 miał instrukcje warunkowego rozgałęzienia i powrotu z podprogramu:

- BSTR i BSTA: rozgałęzienie do podprogramu na warunku True (zero, więcej niż, mniej niż lub bezwarunkowo) z adresowaniem względnym lub bezwzględnym

- BSFR i BSFA: rozgałęzienie do podprogramu pod warunkiem Fałsz (zero, więcej niż lub mniej niż) z adresowaniem względnym lub bezwzględnym

- BSNR i BSNA: rozgałęzienie do podprogramu, jeśli rejestr jest niezerowy (R0, R1, R2 lub R3) z adresowaniem względnym lub bezwzględnym

- RETC: powrót z podprogramu na warunku True (zero, większy niż, mniejszy niż lub bezwarunkowy)

- RETE: powrót z przerwania na warunku True (zero, większy niż, mniejszy niż lub bezwarunkowy)

- ZBSR: gałąź do podprogramu względem adresu zero

- BSXA: indeksowanie gałęzi do podprogramu

Tylko instrukcje rozgałęzienia wykorzystujące adresowanie bezwzględne wykorzystywały wszystkie 15 bitów pola adresu jako adres. Użycie takiej instrukcji rozgałęzienia było więc jedynym sposobem na ustawienie dwóch bitów w rejestrze strony (sterowanie bitami 14 i 13 szyny adresowej) i zmianę aktualnej strony 8 KB.

Wersje

- 2650 oryginalna wersja z maksymalną częstotliwością zegara 1,25 MHz

- Ulepszona wersja 2650A (niewielkie zmiany produkcyjne w celu poprawy stabilności) Maksymalna częstotliwość zegara 1,25 MHz

- 2650A-1 jako 2650A z maksymalną częstotliwością zegara 2 MHz

- 2650B

- 2650B-1 jako 2650B z maksymalną częstotliwością zegara 2 MHz

2650B miał następujące zmiany i ulepszenia w stosunku do 2650A:

- Dwa nowe sygnały – „Bus Enable” na pinie 15 i „Cycle Last” na pinie 25.

- Program Status Word Górne bity 3 i 4 są ustawialnymi i testowalnymi flagami użytkownika (nieużywane w 2650A).

- Dwie nowe instrukcje do zapisywania i przywracania dolnego rejestru stanu w celu uproszczenia przetwarzania przerwań.

- Instrukcje rejestru jednobajtowego R0 wykonują się szybciej (jeden cykl zamiast dwóch).

Drugie źródła

W 1975 roku Signetics został sprzedany firmie Philips , a 2650 został później włączony do linii Philips Semiconductors . Zrobili wersję 2650 o nazwie MAB2650A. Valvo, spółka zależna firmy Philips, sprzedała model 2650 w Niemczech. Firma Valvo sprzedała również jednopłytowy komputer VA200 (Eurocard) 2650 z 4 KB PROM/EPROM, 1 KB RAM i czterema portami we/wy.

Innymi producentami licencjonowanych kopii chipa byli Harris i Intersil .

Chipy peryferyjne

Model 2650 był dostarczany z pełnym zestawem układów peryferyjnych:

- Koder wideo 2621 (PAL)

- Koder wideo 2622 (NTSC)

- 2636 Programowalny interfejs wideo

- 2637 Uniwersalny interfejs wideo

- 2651 Programowalny interfejs komunikacyjny

- Obwód komunikacji wieloprotokołowej 2652 (w tym sterowanie synchronicznym łączem danych (SDLC))

- 2653 Generator wielomianów / kontroler

- 2655 Programowalny interfejs peryferyjny

- 2656 SMI (interfejs pamięci systemowej)

- 2657 Bezpośredni dostęp do pamięci

- 2661 Rozszerzony programowalny interfejs komunikacyjny (EPCI)

- 2670 Wyświetl generator znaków i grafiki

- 2671 Programowalna klawiatura i kontroler komunikacyjny

- 2672 Programowalny kontroler taktowania wideo

- 2673 Kontroler atrybutów wideo

Wiele z tych układów peryferyjnych zostało zaprojektowanych tak, aby można ich było używać z innymi mikroprocesorami, na przykład arkusz danych 2672 sugeruje użycie go z mikrokontrolerem Intel 8048 .

Philips Technical Note 083 opisuje, jak podłączyć 2651 PCI do różnych innych mikroprocesorów, takich jak 8080, 8085, Z80, 8048 i 6800

Potomkowie układów komunikacji szeregowej 2651/2661 są nadal sprzedawane jako seria Philips SC26.

2656 Interfejs pamięci systemowej

Model 2656 został specjalnie zaprojektowany w celu rozszerzenia i połączenia z modelem 2650 oraz umożliwienia stworzenia komputera z dwoma układami scalonymi. Zawierał wszystko, czego brakowało 2650 do stworzenia kompletnego komputera:

- 2 KB 8-bitowej pamięci programu ROM z zaprogramowaną maską

- 128 bajtów 8-bitowej pamięci RAM

- Generator zegara z siecią kryształową lub RC

- Resetowanie po włączeniu

- Osiem pinów we/wy ogólnego przeznaczenia

Piny we/wy mogą być używane jako 8-bitowe porty we/wy lub zaprogramowane do generowania sygnałów włączających dodatkową pamięć RAM, ROM lub porty we/wy. Osiągnięto to poprzez programowanie masek programowalnej tablicy logicznej w 2656.

Aby opracować i przetestować projekt przed przekazaniem go do produkcji, firma Philips sprzedała PC4000, płytkę emulatora 2656 wykorzystującą PROM i FPLA do emulacji pamięci ROM i PLA w 2656.

Notatki

Cytaty

Bibliografia

- Rowe, Jamieson (wrzesień 1976). „Signetics 2650” (PDF) . Elektronika Australia .

Linki zewnętrzne

- 2650 emulatorów

- Arkusz danych

- Świat procesorów z rodziny Signetics 2650

- Instruktor 50 Old-computers.com

- Adaptowalny system rozwoju komputera pokładowego wraz z monitorem 1 KiB PipBug i 512 bajtami pamięci RAM

- 2650 na www.cpu-museum.com (archiwum)

- Płytka Electronics Australia 2650 na Yesterdaystechnology.com

- Retrospektywa Signetics 2650: An IBM on a Chip w The CPUSHACK Museum (16 października 2016)

- Zaccaria The Invaders w Museum of the Game

- Asembler krzyżowy 2650 jest dostępny na stronie https://shop-pdp.net/index.php