Logika PMOS

PMOS lub pMOS (od p-kanałowego metal-tlenek-półprzewodnik ) to rodzina obwodów cyfrowych opartych na tranzystorach polowych z efektem p-kanałowym w trybie wzmocnienia metal- tlenek -półprzewodnik (MOSFET). W późnych latach sześćdziesiątych i wczesnych siedemdziesiątych XX wieku logika PMOS była dominującą technologią półprzewodnikową w wielkoskalowych układach scalonych, zanim została zastąpiona przez urządzenia NMOS i CMOS .

Historia i zastosowanie

Mohamed Atalla i Dawon Kahng wyprodukowali pierwszy działający MOSFET w Bell Labs w 1959 roku. Wyprodukowali zarówno urządzenia PMOS, jak i NMOS, ale działały tylko urządzenia PMOS. Minie ponad dekada, zanim zanieczyszczenia w procesie produkcyjnym (zwłaszcza sód) będą mogły być wystarczająco dobrze zarządzane, aby wyprodukować praktyczne urządzenia NMOS.

W porównaniu z bipolarnym tranzystorem złączowym , jedynym innym urządzeniem dostępnym w tamtym czasie do użytku w układzie scalonym , MOSFET oferuje szereg zalet:

- Biorąc pod uwagę procesy wytwarzania urządzeń półprzewodnikowych o podobnej precyzji, MOSFET wymaga tylko 10% powierzchni bipolarnego tranzystora złączowego. Głównym powodem jest to, że MOSFET jest samoizolujący i nie wymaga izolacji złącza p-n od sąsiednich komponentów na chipie.

- MOSFET wymaga mniej etapów procesu i dlatego jest prostszy i tańszy w produkcji (jeden etap domieszkowania dyfuzyjnego w porównaniu do czterech w przypadku procesu bipolarnego).

- Ponieważ dla tranzystora MOSFET nie występuje statyczny prąd bramki, pobór mocy układu scalonego opartego na tranzystorach MOSFET może być niższy.

Wady w stosunku do bipolarnych układów scalonych to:

- Szybkość przełączania była znacznie niższa ze względu na duże pojemności bramek .

- Wysokie napięcie progowe wczesnych tranzystorów MOSFET prowadziło do wyższego minimalnego napięcia zasilania (od -24 V do -28 V).

Firma General Microelectronics wprowadziła pierwszy komercyjny obwód PMOS w 1964 r., 20-bitowy rejestr przesuwny ze 120 tranzystorami MOSFET – jak na tamte czasy poziom integracji był niewiarygodny. Próba General Microelectronics w 1965 roku, aby opracować zestaw 23 niestandardowych układów scalonych do elektronicznego kalkulatora dla Victor Comptometer , okazała się zbyt ambitna, biorąc pod uwagę niezawodność obwodów PMOS w tamtym czasie i ostatecznie doprowadziła do upadku General Microelectronics. Inne firmy kontynuowały produkcję obwodów PMOS, takich jak duże rejestry przesuwne ( General Instrument ) czy multiplekser analogowy 3705 ( Fairchild Semiconductor ), które nie były możliwe w ówczesnych technologiach bipolarnych.

Znacząca poprawa nastąpiła wraz z wprowadzeniem technologii samonastawnych bramek polikrzemowych w 1968 roku. Tom Klein i Federico Faggin z Fairchild Semiconductor ulepszyli proces samonastawnych bramek, aby uczynić go opłacalnym komercyjnie, co zaowocowało wypuszczeniem analogowego multipleksera 3708 jako pierwszy układ scalony z bramką krzemową. Proces samonastawnej bramki pozwolił na ściślejsze tolerancje produkcyjne, a tym samym zarówno mniejsze tranzystory MOSFET, jak i zmniejszoną, stałą pojemność bramki. Na przykład w przypadku pamięci PMOS ta technologia zapewnia trzy do pięciu razy większą prędkość w połowie obszaru chipa. Polikrzemowy materiał bramki nie tylko umożliwił samonastawną bramkę, ale także obniżył napięcie progowe, aw konsekwencji niższe minimalne napięcie zasilania (np. -16 V), zmniejszając zużycie energii. Ze względu na niższe napięcie zasilania często określa się logikę PMOS z bramką krzemową niskonapięciowy PMOS w przeciwieństwie do starszego PMOS z metalową bramką jako wysokonapięciowy PMOS .

Z różnych powodów Fairchild Semiconductor nie rozwijał układów scalonych PMOS tak intensywnie, jak chcieli zaangażowani menedżerowie. Dwóch z nich, Gordon Moore i Robert Noyce , zdecydowało się w 1968 roku założyć zamiast tego własny startup – Intel . Wkrótce potem dołączyli do nich inni inżynierowie Fairchild, w tym Federico Faggin i Les Vadasz . Intel wprowadził swoją pierwszą statyczną pamięć o dostępie swobodnym PMOS o pojemności 256 bitów, Intel 1101, w 1969 r. 1024-bitowa dynamiczna pamięć o dostępie swobodnym Intel 1103 nastąpił w 1970 roku. Model 1103 odniósł komercyjny sukces i szybko zaczął zastępować pamięć z rdzeniem magnetycznym w komputerach. Intel wprowadził swój pierwszy mikroprocesor PMOS , Intel 4004 , w 1971 roku. Wiele firm poszło w ślady Intela. Większość wczesnych mikroprocesorów produkowano w technologii PMOS: 4040 i 8008 firmy Intel; IMP-16 , PACE i SC/MP z National Semiconductor ; TMS1000 firmy Texas Instruments ; PPS-4 i PPS-8 firmy Rockwell International . Na tej liście mikroprocesorów znajduje się kilka komercyjnych nowości: pierwszy 4-bitowy mikroprocesor (4004), pierwszy 8-bitowy mikroprocesor (8008), pierwszy jednoukładowy 16-bitowy mikroprocesor (PACE) i pierwszy jednoukładowy 4-bitowy mikrokontroler (TMS1000; RAM i ROM na tym samym chipie co procesor ).

Do 1972 roku technologia NMOS została ostatecznie rozwinięta do punktu, w którym można ją było stosować w produktach komercyjnych. Zarówno Intel (z 2102), jak i IBM wprowadziły układy pamięci 1 kbit. Ponieważ ruchliwość elektronów w kanale typu n tranzystorów MOSFET NMOS jest około trzy razy większa niż w otworze mobilność w kanale typu p tranzystorów PMOS MOSFET, logika NMOS pozwala na zwiększenie szybkości przełączania. Z tego powodu logika NMOS szybko zaczęła zastępować logikę PMOS. Pod koniec lat siedemdziesiątych mikroprocesory NMOS wyprzedziły procesory PMOS. Logika PMOS pozostawała w użyciu przez jakiś czas ze względu na niski koszt i stosunkowo wysoki poziom integracji w aplikacjach takich jak proste kalkulatory i zegary. CMOS obiecywała drastycznie niższe zużycie energii niż PMOS lub NMOS. Mimo że układ CMOS został zaproponowany już w 1963 roku przez Franka Wanlassa i komercyjną serię 4000 Układy scalone CMOS weszły do produkcji w 1968 r., CMOS pozostawał skomplikowany w produkcji i nie pozwalał ani na poziom integracji PMOS czy NMOS, ani na szybkość NMOS. Dopiero w latach 80. CMOS zastąpił NMOS jako główną technologię mikroprocesorów.

Opis

Obwody PMOS mają szereg wad w porównaniu z alternatywami NMOS i CMOS , w tym konieczność stosowania kilku różnych napięć zasilania (zarówno dodatnich, jak i ujemnych), duże rozpraszanie mocy w stanie przewodzącym i stosunkowo duże cechy. Ponadto ogólna prędkość przełączania jest niższa.

PMOS wykorzystuje tranzystory polowe z kanałem p (+) metal-tlenek-półprzewodnik (MOSFET) do implementacji bramek logicznych i innych obwodów cyfrowych . Tranzystory PMOS działają poprzez tworzenie warstwy inwersyjnej w korpusie tranzystora typu n . Ta warstwa inwersyjna, zwana kanałem p, może przewodzić dziury między zaciskami „źródła” i „drenu” typu p .

Kanał p jest tworzony przez przyłożenie ujemnego napięcia (wspólne było -25 V) do trzeciego zacisku, zwanego bramką. Podobnie jak inne tranzystory MOSFET, tranzystory PMOS mają cztery tryby działania: odcięcie (lub podprog), trioda, nasycenie (czasami nazywane aktywnym) i nasycenie prędkości.

Chociaż układ logiczny PMOS jest łatwy do zaprojektowania i wyprodukowania (MOSFET może działać jako rezystor, więc cały obwód może być wykonany z tranzystorów PMOS FET), ma również kilka wad. Najgorszym problemem jest to, że przez bramkę logiczną PMOS płynie prąd stały, gdy aktywna jest tzw . nawet wtedy, gdy obwód jest bezczynny.

Ponadto obwody PMOS wolno przechodzą z wysokiego na niski. Podczas przejścia z niskiego na wysoki tranzystory zapewniają niską rezystancję, a ładunek pojemnościowy na wyjściu gromadzi się bardzo szybko (podobnie jak ładowanie kondensatora przez bardzo niską rezystancję). Ale rezystancja między wyjściem a ujemną szyną zasilającą jest znacznie większa, więc przejście z wysokiego na niski trwa dłużej (podobnie jak rozładowanie kondensatora przez wysoką rezystancję). Zastosowanie rezystora o niższej wartości przyspieszy proces, ale także zwiększy rozpraszanie mocy statycznej.

Dodatkowo asymetryczne poziomy logiczne wejść sprawiają, że obwody PMOS są podatne na zakłócenia.

Większość układów scalonych PMOS wymaga zasilania 17-24 V DC. Jednak mikroprocesor Intel 4004 PMOS wykorzystuje logikę PMOS z bramkami polikrzemowymi , a nie metalowymi , co pozwala na mniejszą różnicę napięć. Aby zapewnić kompatybilność z TTL , 4004 wykorzystuje dodatnie napięcie zasilania VSS = +5V i ujemne napięcie zasilania VDD = -10V.

Bramy

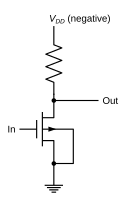

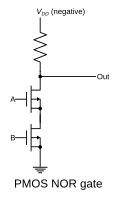

Tranzystory MOSFET typu p są rozmieszczone w tak zwanej „sieci podciągającej” (PUN) między wyjściem bramki logicznej a dodatnim napięciem zasilania, podczas gdy rezystor jest umieszczony między wyjściem bramki logicznej a ujemnym napięciem zasilania. Obwód jest zaprojektowany w taki sposób, że jeśli żądane wyjście jest wysokie, wówczas PUN będzie aktywny, tworząc ścieżkę prądową między dodatnim zasilaniem a wyjściem.

Bramki PMOS mają taki sam układ jak bramki NMOS, jeśli wszystkie napięcia są odwrócone. Zatem dla logiki aktywnej-wysokiej prawa De Morgana pokazują, że bramka PMOS NOR ma taką samą strukturę jak bramka NMOS NAND i odwrotnie.

Falownik PMOS z rezystorem obciążenia.

|

Bramka PMOS NAND z rezystorem obciążenia.

|

Bramka PMOS NOR z rezystorem obciążenia.

|

Dalsza lektura

- Savard, John JG (2018) [2005]. „Z czego zbudowane są komputery” . czworokąt . Zarchiwizowane od oryginału w dniu 2018-07-02 . Źródło 2018-07-16 .