Logika czterofazowa

Logika czterofazowa jest rodzajem i metodologią projektowania logiki dynamicznej . Umożliwiło to niewyspecjalizowanym inżynierom projektowanie dość złożonych układów scalonych przy użyciu procesów PMOS lub NMOS . Wykorzystuje rodzaj 4-fazowego sygnału zegarowego .

Historia

RK „Bob” Booher, inżynier z Autonetics , wynalazł logikę czterofazową i przekazał ten pomysł Frankowi Wanlassowi z Fairchild Semiconductor ; Wanlass promował tę formę logiki w General Instrument Microelectronics Division. Booher stworzył pierwszy działający czterofazowy układ scalony, integrator Autonetics DDA , w lutym 1966 roku; później zaprojektował kilka chipów i zbudował Autonetics D200 przy użyciu tej techniki.

W kwietniu 1967 roku Joel Karp i Elizabeth de Atley opublikowali artykuł „Użyj czterofazowej logiki MOS IC” w czasopiśmie Electronic Design . W tym samym roku Cohen, Rubenstein i Wanlass opublikowali „Czterofazowe systemy zegarowe MTOS”. Wanlass był dyrektorem ds. badań i inżynierii w General Instrument Microelectronics Division w Nowym Jorku od czasu opuszczenia Fairchild Semiconductor w 1964 roku.

Lee Boysel , uczeń Wanlassa i projektant w Fairchild Semiconductor , a później założyciel Four-Phase Systems , wygłosił „późne wiadomości” na temat czterofazowego 8-bitowego sumatora w październiku 1967 roku na spotkaniu International Electron Devices. JL Seely, kierownik operacji MOS w General Instrument Microelectronics Division, również pisał o logice czterofazowej pod koniec 1967 roku.

W 1968 roku Boysel opublikował artykuł „Adder on a Chip: LSI pomaga obniżyć koszty małej maszyny” w czasopiśmie Electronics ; W tym roku pojawiają się również artykuły czterofazowe z YT Yen. Wkrótce pojawiły się inne dokumenty.

Boysel wspomina, że czterofazowa logika dynamiczna pozwoliła mu osiągnąć 10-krotną gęstość upakowania, 10-krotną prędkość i 1/10 mocy w porównaniu z innymi technikami MOS używanymi w tamtym czasie (logika PMOS z metalową bramką nasyconego obciążenia ) , używając proces MOS pierwszej generacji w firmie Fairchild.

Struktura

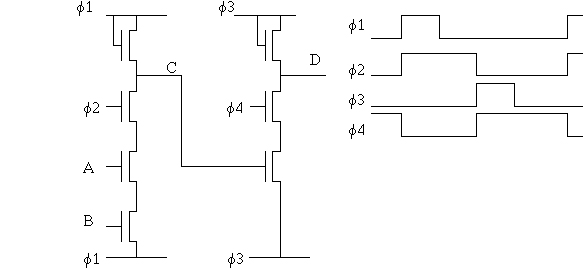

Zasadniczo istnieją dwa rodzaje bramek logicznych – bramka „1” i bramka „3”. Różnią się one tylko fazami zegara używanymi do ich napędzania. Bramka może mieć dowolną funkcję logiczną; więc potencjalnie każda bramka ma dostosowany układ. Przykładową 2-wejściową bramkę NAND 1 i bramkę falownika 3 wraz z ich fazami zegara (przykład wykorzystuje tranzystory NMOS) pokazano poniżej:

Zegary ϕ1 i ϕ3 nie mogą się nakładać, podobnie jak zegary ϕ2 i ϕ4. Biorąc pod uwagę bramkę 1, podczas wysokiego czasu zegara ϕ1 (znanego również jako wstępnego ładowania ) wyjście C ładuje się wstępnie do V(ϕ1)−Vth , gdzie Vth reprezentuje próg wstępnego naładowania tranzystora. Podczas następnego kwadransowego cyklu zegarowego ( próbkowania ), gdy φ1 jest niskie, a ϕ2 jest wysokie, C albo pozostaje w stanie wysokim (jeśli A lub B są w stanie niskim), albo C rozładowuje się w stanie niskim (jeśli A i B są w stanie wysokim).

Wejścia A i B muszą być stabilne przez cały ten czas próbkowania. Wyjście C staje się ważne w tym czasie – i dlatego wyjście 1 bramki nie może sterować wejściami innej 1 bramki. Stąd 1 bramka musi zasilić 3 bramki, a one z kolei muszą zasilić 1 bramkę.

Przydaje się jeszcze jedna rzecz – 2 i 4 bramki. Wstępne ładowanie bramki 2 na ϕ1 i próbki na ϕ3:

i 4 ładunki bramkowe na ϕ3 i próbki na φ1.

Zasady łączenia bramek są następujące: 1 bramka może sterować 2 bramkami i/lub 3 bramkami; 2 bramki mogą sterować tylko 3 bramkami, 3 bramki mogą sterować 4 bramkami i/lub 1 bramką, 4 bramki mogą sterować tylko 1 bramką:

Stosowanie

Logika czterofazowa działa dobrze; w szczególności nie ma zagrożeń związanych z wyścigiem, ponieważ każda kombinacyjna bramka logiczna zawiera rejestr. Warto zaznaczyć, że układ nie wymaga szynowania żadnych zasilaczy – szynoprzewodowane są jedynie linie zegarowe. Ponadto, ponieważ technika projektowania jest bezproporcjonalna (por. logika statyczna ), wiele projektów może wykorzystywać tranzystory o minimalnej wielkości.

Istnieją pewne trudności:

- Wyjście bramki jest dynamiczne. Oznacza to, że jego stan jest utrzymywany na pojemności na wyjściu bramki. Ale ścieżka wyjściowa może przecinać linie zegara i inne wyjścia bramek, z których wszystkie mogą zmieniać ładunek na kondensatorze. Aby napięcie wyjściowe bramki pozostawało na pewnym bezpiecznym poziomie 0 lub 1 podczas cyklu, należy obliczyć wielkość zmiany i, jeśli to konieczne, dodać dodatkową (dyfuzyjną) pojemność do węzła wyjściowego.

- Dla danego napięcia zasilania, procesu i częstotliwości zegara projektant musi wykonać pewne obliczenia, aby inżynierowie układu mogli z kolei wykonać obliczenia w celu obliczenia pojemności „zbiorczej” potrzebnej dla każdej bramki. Bramka z dużym obciążeniem pojemnościowym może wymagać tranzystorów wejściowych większych niż minimalne (aby obciążenie mogło zostać rozładowane na czas). To z kolei zwiększa obciążenie bramek sterujących wejściami tej bramki. Może się więc zdarzyć, zwłaszcza w konstrukcjach o wysokiej częstotliwości, że rozmiar bramki będzie się zwiększał, jeśli docelowa prędkość jest zbyt agresywna.

Pierwszy kalkulator elektroniczny zbudowany z wielkoskalowych układów scalonych (LSI), Sharp QT-8D z 1969 roku, wykorzystywał logikę 4-fazową, która została wyprodukowana przez Rockwell International , ponieważ Japonia nie miała jeszcze technologii LSI, aby zrobić to w kraju. Logika 4-fazowa była również rozważana do użycia w Intel 4004 , ale tylko Rockwell miał wówczas narzędzia do projektowania i wiedzę specjalistyczną do tworzenia 4-fazowych układów scalonych na dużą skalę, więc Intel zdecydował się zamiast tego na logikę dynamiczną 2-fazową.

Ewolucja

Wraz z pojawieniem się CMOS , tranzystor wstępnego ładowania można zmienić, aby był uzupełnieniem typu tranzystora logicznego, co pozwala na szybkie ładowanie wyjścia bramki aż do wysokiego poziomu linii zegara, poprawiając w ten sposób prędkość, wahania sygnału , zużycie energii i margines szumów. Ta technika jest używana w logice domina .