TurboSPARC

| |

| Informacje ogólne | |

|---|---|

| Wystrzelony | 1996 |

| Zaprojektowany przez | Fujitsu Microelectronics, Inc. |

| Wydajność | |

| Maks. Częstotliwość taktowania procesora | 160 MHz do 180 MHz |

| Architektura i klasyfikacja | |

| Zestaw instrukcji | SPARC V8 |

| Specyfikacje fizyczne | |

| Rdzenie |

|

TurboSPARC to mikroprocesor , który implementuje architekturę zestawu instrukcji SPARC V8 ( ISA) opracowaną przez Fujitsu Microelectronics, Inc. (FMI), amerykańską spółkę zależną japońskiej międzynarodowej firmy zajmującej się sprzętem i usługami informatycznymi Fujitsu Limited z siedzibą w San Jose w Kalifornii . Był to mikroprocesor z niższej półki, opracowany głównie jako aktualizacja dla stacji roboczej SPARCstation 5 opartej na microSPARC-II firmy Sun Microsystems . Został wprowadzony 30 września 1996 r. W wersji 170 MHz w cenie 499 USD w ilości 1000 sztuk. TurboSPARC został w większości zastąpiony na rynku SPARC z niższej półki przez UltraSPARC IIi pod koniec 1997 roku, ale pozostał dostępny.

Użytkownikami TurboSPARC byli Force Computers, Fujitsu , RDI Computer, Opus Systems, Tadpole Technologies , Tatung Science and Technology oraz Themis Computers. Fujitsu używało wersji 160 MHz w SPARCstation 5 , podczas gdy inne firmy używały wersji 170 MHz w stacjach roboczych, notebookach i komputerach wbudowanych.

Wydajność procesora TurboSPARC 170 MHz była podobna do wydajności procesora Intel Pentium 120 MHz , ale w porównaniu z procesorem microSPARC-II taktowanym zegarem 110 MHz miał dwa razy większą wydajność na liczbach całkowitych i półtora raza większą wydajność na liczbach zmiennoprzecinkowych.

Opis

TurboSPARC był prostym skalarnym projektem w kolejności. Na etapie pobierania dwie instrukcje zostały pobrane z 16 KB bezpośrednio odwzorowanej pamięci podręcznej instrukcji. Podczas etapu dekodowania jedna instrukcja była dekodowana, a jej operandy odczytywane z pliku rejestru. Egzekucja rozpoczęła się w trzecim etapie. TurboSPARC miał jednostkę całkowitą i jednostkę zmiennoprzecinkową . Większość instrukcji arytmetycznych na liczbach całkowitych, z wyjątkiem mnożenia i dzielenia, ma opóźnienie jednego cyklu. Mnożenie i dzielenie zostało wykonane przez FPU. Mnożenie miało opóźnienie w siedmiu cyklach, podczas gdy w przypadku dzielenia opóźnienie wynosiło od 8 do 33 cykli. Większość instrukcji arytmetycznych zmiennoprzecinkowych, z wyjątkiem dzielenia i pierwiastkowania, miała czterocyklowe opóźnienie.

Dostęp do pamięci następuje podczas etapu czwartego. TurboSPARC ma 16 KB pamięci podręcznej danych. Pamięć podręczna jest mapowana bezpośrednio i wykorzystuje zasady zapisu wstecznego. W przypadku trafienia w pamięci podręcznej dane są zwracane w tym samym cyklu i sprawdzane pod kątem błędów podczas etapu piątego. Wyniki i obciążenia w postaci liczb całkowitych są zapisywane do pliku rejestru podczas etapu szóstego. Instrukcje zmiennoprzecinkowe, które zajmują więcej cykli, są zakończone na etapie siódmym i zapisywane do pliku rejestru zmiennoprzecinkowego na etapie ósmym.

TurboSPARC miał zintegrowane kontrolery dla pamięci podręcznej L2, pamięci, interfejsu AFX i interfejsu SBus. Obsługiwana była zewnętrzna pamięć podręczna L2 o pojemności 256 KB, 512 KB lub 1 MB. Pamięć podręczna działała z połową lub jedną trzecią częstotliwości zegara wewnętrznego: odpowiednio 85 lub 56,67 MHz przy 170 MHz. Był mapowany bezpośrednio, miał 32-bajtowy rozmiar linii i stosował zasady zapisu z możliwością zapisu. Był chroniony przez parytet. Pamięć podręczna została zbudowana z 12 ns potokowej pamięci o dostępie swobodnym (PBSRAM). Kontroler pamięci obsługiwał od 8 do 256 MB trybu szybkiego stronicowania (FPM) DRAM w ośmiu bankach. Dostęp do pamięci podręcznej i pamięci L2 uzyskiwano za pomocą magistrali systemowej, 72-bitowej magistrali, z której 64 bity były przeznaczone na dane.

Interfejs AFX umożliwił kartom graficznym AFX bezpośredni dostęp do pamięci. Dzieli tę samą magistralę danych z pamięcią podręczną i kontrolerami pamięci, ale używa własnych linii sterujących. Kontroler SBus miał własny 16-wejściowy bufor translacji wejścia/wyjścia. TurboSPARC obsługiwał SBus od 16,67 do 25 MHz. TurboSPARC nie był przystosowany do obsługi wielu procesorów.

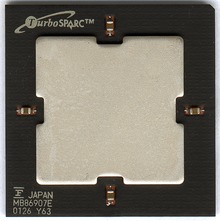

TurboSPARC zawierał 3,0 miliony tranzystorów i mierzył 11,5 na 11,5 mm dla powierzchni matrycy 132,25 mm2 . Został wyprodukowany przez firmę Fujitsu w procesie CS-60ALE, czteropoziomowym procesie metal -tlenek-półprzewodnik (CMOS) o grubości 0,35 µm. TurboSPARC został zapakowany w 416-kulkową plastikową siatkę (PBGA). Używał zasilacza 3,3 V i miał maksymalne rozpraszanie mocy 9 W.

Notatki

- Fujitsu Microelectronics, Inc. (30 września 1996). Nowy procesor Fujitsu Microelectronics TurboSPARC wyznacza nowy poziom wydajności dla stacji roboczych z niższej półki i średniej klasy . Informacja prasowa .

- Gwennap, Linley (18 listopada 1996). „TurboSPARC oferuje ulepszenia z niższej półki” . Raport mikroprocesorowy , s. 14–16.