Bramka LUB

Bramka OR jest cyfrową bramką logiczną , która implementuje alternatywę logiczną . Bramka OR zwraca wartość true, jeśli jedno lub oba jej wejścia są prawdziwe; w przeciwnym razie zwraca false. Stany wejściowe i wyjściowe są zwykle reprezentowane przez różne napięcia .

Opis

| Tabela prawdy bramki OR | ||

|---|---|---|

| Wejście | Wyjście | |

| A | B | A LUB B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Bramka akceptuje dwa wejścia . Wyprowadza 1, jeśli jedno lub oba te wejścia są równe 1, lub wyprowadza 0 tylko wtedy, gdy oba wejścia są równe 0. Wejścia i wyjścia są cyframi binarnymi („ bitami ”), które mają dwa możliwe stany logiczne . Oprócz 1 i 0, stany te można nazwać prawdziwymi i fałszywymi, wysokimi i niskimi, aktywnymi i nieaktywnymi lub innymi takimi parami symboli.

W ten sposób wykonuje logiczne rozłączenie (∨) z logiki matematycznej . Bramkę można przedstawić za pomocą znaku plus (+), ponieważ można jej użyć do logicznego dodawania . Równoważnie, bramka OR znajduje maksimum między dwiema cyframi binarnymi, tak jak bramka AND znajduje minimum .

Wraz z bramką AND i bramką NOT bramka OR jest jedną z trzech podstawowych bramek logicznych, z których można zbudować dowolny obwód boolowski . Wszystkie inne bramki logiczne mogą być wykonane z tych trzech bramek; za ich pomocą można zaimplementować dowolną funkcję w matematyce binarnej.

Czasami nazywa się to bramką włączającą OR, aby odróżnić ją od XOR , wyłącznej bramki OR. Zachowanie OR jest takie samo jak XOR, z wyjątkiem przypadku 1 dla obu wejść. W sytuacjach, w których to nigdy nie występuje (na przykład w pełnym sumatorze ) dwa typy bramek są wymienne. To podstawienie jest wygodne, gdy obwód jest realizowany przy użyciu prostych układów scalonych , które zawierają tylko jeden typ bramki na układ.

Symbolika

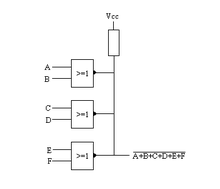

istnieją dwa symbole bramek logicznych reprezentujące bramkę OR: symbol amerykański ( ANSI lub „wojskowy”) i symbol IEC („europejski” lub „prostokątny”). Symbol DIN jest przestarzały.

„≥1” na symbolu ICE wskazuje, że wyjście jest aktywowane przez co najmniej jedno aktywne wejście.

Opis sprzętu i pinout

Bramki OR są podstawowymi bramkami logicznymi i są dostępne w rodzinach logicznych układów scalonych TTL i CMOS . Standardowym CMOS serii 4000 jest układ 4071, który zawiera cztery niezależne dwuwejściowe bramki OR. Urządzenie TTL to 7432. Istnieje wiele odgałęzień oryginalnej bramki 7432 OR, wszystkie mają ten sam układ pinów, ale inną architekturę wewnętrzną, co pozwala im działać w różnych zakresach napięcia i/lub przy wyższych prędkościach. Oprócz standardowej 2-wejściowej bramki OR dostępne są również 3- i 4-wejściowe bramki OR. W serii CMOS są to:

- 4075: potrójna 3-wejściowa bramka OR

- 4072: podwójna 4-wejściowa bramka OR

Odmiany obejmują:

- 74LS32: poczwórna 2-wejściowa bramka OR ( wersja Schottky'ego o małej mocy)

- 74HC32: poczwórna 2-wejściowa bramka OR (wersja CMOS o dużej szybkości) — ma niższy pobór prądu/szerszy zakres napięcia

- 74AC32: poczwórna 2-wejściowa bramka OR (zaawansowana wersja CMOS) - podobna do 74HC32, ale ze znacznie szybszymi prędkościami przełączania i mocniejszym napędem

- 74LVC32: niskonapięciowa wersja CMOS tego samego.

Implementacje

Reprezentacja analityczna

jest analityczną reprezentacją bramki OR:

Alternatywy

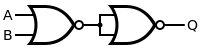

Jeśli nie są dostępne żadne określone bramki OR, można je wykonać z bramek NAND lub NOR w konfiguracji pokazanej na poniższym obrazku. Dowolna bramka logiczna może być zbudowana z kombinacji NAND lub NOR .

| Wymarzona brama | Konstrukcja NAND | Konstrukcja NOR |

|---|---|---|

|

|

|

Przewodowy-OR

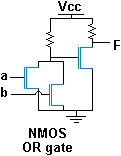

W przypadku aktywnych wyjść logicznych typu otwarty kolektor , używanych do sygnałów sterujących w wielu obwodach, funkcję OR można uzyskać, łącząc ze sobą kilka wyjść. Taki układ nazywa się przewodowym LUB . Ta implementacja funkcji OR zazwyczaj występuje również w układach scalonych procesów tranzystorowych typu N lub P.