Goodyear MPP

Goodyear Massively Parallel Processor ( MPP ) był masowo równoległym superkomputerem zbudowanym przez Goodyear Aerospace dla NASA Goddard Space Flight Center . Został zaprojektowany w celu zapewnienia ogromnej mocy obliczeniowej przy niższych kosztach niż inne istniejące architektury superkomputerów, dzięki wykorzystaniu tysięcy prostych elementów przetwarzających zamiast jednego lub kilku bardzo złożonych procesorów . Rozwój MPP rozpoczął się około 1979 roku; został dostarczony w maju 1983 roku i był w powszechnym użyciu od 1985 do 1991 roku.

Opierał się na wcześniejszym procesorze macierzy STARAN firmy Goodyear , komputerze 4x256 z 1-bitowym elementem przetwarzającym (PE). MPP była dwuwymiarową tablicą 128x128 PE o szerokości 1 bitu. W rzeczywistości PE 132x128 zostały skonfigurowane z dodaną konfiguracją 4x128 w celu zapewnienia odporności na awarie w celu zastąpienia do 4 rzędów (lub kolumn) procesorów w przypadku wystąpienia problemów. PE działały w jednej instrukcji, wielu danych (SIMD) - każdy PE wykonywał tę samą operację jednocześnie, na różnych elementach danych, pod kontrolą mikroprogramowanej jednostki sterującej.

Po przejściu MPP na emeryturę w 1991 r. został przekazany Smithsonian Institution i obecnie znajduje się w zbiorach Centrum Stevena F. Udvara-Hazy'ego Narodowego Muzeum Lotnictwa i Kosmosu . Został zastąpiony w Goddard przez masywnie równoległe komputery MasPar MP-1 i Cray T3D .

Aplikacje

MPP został początkowo opracowany do szybkiej analizy zdjęć satelitarnych . We wczesnych testach był w stanie wyodrębnić i oddzielić różne obszary użytkowania gruntów na Landsat w 18 sekund, w porównaniu z 7 godzinami na DEC VAX-11/780 .

Gdy system został oddany do użytku produkcyjnego, Biuro Nauk Kosmicznych i Zastosowań NASA zwróciło się do naukowców z całego kraju z propozycjami przetestowania i wdrożenia szerokiej gamy algorytmów obliczeniowych w MPP. zaakceptowano 40 projektów tworzących „Grupę Roboczą MPP”; wyniki większości z nich zostały zaprezentowane na Pierwszym Sympozjum o Granicach Obliczeń Masowo Równoległych w 1986 roku.

Niektóre przykłady aplikacji, które zostały wykonane z MPP to:

- Przetwarzanie sygnału danych radarowych z syntetyczną aperturą

- Generowanie map topograficznych poprzez stereoanalizę zdjęć satelitarnych

- Matematyczne modelowanie cyrkulacji oceanicznej

- Grafika komputerowa oparta na ray tracingu

- Sieci neuronowe

- Rozwiązywanie dużych układów równań liniowych

- Symulacja transportu cząstek naładowanych promieniami kosmicznymi

- Zestawy Mandelbrota o wysokiej rozdzielczości

Architektura systemu

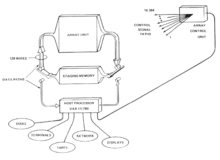

Cały sprzęt MPP składał się z jednostki macierzowej, jednostki sterującej macierzą, pamięci przemieszczania i procesora hosta.

Jednostka Array była sercem MPP, będąc tablicą 128x128 z 16 384 elementami przetwarzającymi. Każdy PE był połączony z czterema najbliższymi sąsiadami - północnym, południowym, wschodnim i zachodnim. Macierz może być skonfigurowana jako płaszczyzna, walec, łańcuch lub torus. PE zostały zaimplementowane na niestandardowym LSI typu krzem na szafirze , który zawierał osiem PE jako podtablicę 2x4. Każdy z PE miał jednostki arytmetyczne i logiczne, 35 rejestrów przesuwnych i 1024 bity pamięci o dostępie swobodnym zaimplementowanej za pomocą gotowych układów pamięci. Procesory pracowały w kawałku bitu sposób i może operować na danych o zmiennej długości. Częstotliwość robocza macierzy wynosiła 10 MHz. Stany magistrali danych wszystkich 16 384 PE zostały połączone w drzewo obejmujące lub logiczne elementy, których pojedyncze wyjście było używane w jednostce sterującej tablicą do operacji, takich jak znajdowanie maksymalnej lub minimalnej wartości tablicy połączonej równolegle. Rejestr w każdym PE kontrolowanym maskowaniem operacji — operacje maskowane były wykonywane tylko na tych PE, w których ten bit rejestru był ustawiony.

Jednostka Sterująca Macierzą (ACU) rozgłasza polecenia i adresy pamięci do wszystkich PE w Jednostce Macierzy i odbiera bity stanu z Jednostki Macierzy. Wykonywał operacje księgowe, takie jak sterowanie pętlą i wywoływanie podprogramów. Kod programu aplikacyjnego był przechowywany w pamięci ACU; ACU wykonała skalarne części programu, a następnie ustawiła w kolejce równoległe instrukcje dla tablicy. Kontrolował również przenoszenie danych między PE oraz między jednostką macierzy a pamięcią przemieszczania.

Pamięć pomostowa była blokiem pamięci o pojemności 32 MB do buforowania danych jednostki macierzy. Było to przydatne, ponieważ same PE miały łącznie tylko 2 MB pamięci (1024 bity na PE) i ponieważ zapewniały wyższą przepływność komunikacji niż połączenie z procesorem hosta (80 megabajtów na sekundę w porównaniu z 5 megabajtami na sekundę). Pamięć pomostowa zapewniała również funkcje manipulacji danymi, takie jak „obracanie rogów” (zmiana kolejności na bajty lub słowa z tablicy) oraz wielowymiarowy dostęp do tablicy. Dane zostały przeniesione między pamięcią pomostową a macierzą za pośrednictwem 128 równoległych linii.

Procesor hosta był komputerem typu front-end, który ładował programy i dane do MPP oraz zapewniał narzędzia programistyczne i dostęp sieciowy do MPP. Oryginalnym procesorem hosta był PDP-11 , który wkrótce został zastąpiony przez VAX-11/780 podłączony do MPP kanałem DR-780. VAX działał pod kontrolą VMS i został zaprogramowany w MPP Pascal.

Szybkość operacji

Surowa prędkość obliczeniowa dla podstawowych operacji arytmetycznych na MPP była następująca:

| Operacja | Miliony operacji na sekundę |

|---|---|

| Dodawanie tablic | |

| 8-bitowe liczby całkowite (suma 9-bitowa) | 6553 |

| 12-bitowe liczby całkowite (suma 13-bitowa) | 4428 |

| 32-bitowe liczby zmiennoprzecinkowe | 430 |

| Mnożenie tablic | |

| 8-bitowe liczby całkowite (produkt 16-bitowy) | 1861 |

| 12-bitowe liczby całkowite (produkt 24-bitowy) | 910 |

| 32-bitowe liczby zmiennoprzecinkowe | 216 |

| Mnożenie tablicy przez skalar | |

| 8-bitowe liczby całkowite (produkt 16-bitowy) | 2340 |

| 12-bitowe liczby całkowite (produkt 24-bitowy) | 1260 |

| 32-bitowe liczby zmiennoprzecinkowe | 373 |

Zobacz też

- Fischer, James R.; Goodyear Aerospace Corporation (1987). „Dodatek B. Podsumowanie techniczne” . Granice masowo równoległych obliczeń naukowych . Krajowa Administracja Aeronautyki i Przestrzeni Kosmicznej, Biuro Informacji Naukowo-Technicznej. s. 289–294 . Źródło 11 czerwca 2012 r .

- Batcher, KE (1 września 1980). „Projekt procesora masowo równoległego”. Transakcje IEEE na komputerach . C-29 (9): 836–840. doi : 10.1109/TC.1980.1675684 . S2CID 13351618 .

- Batcher, Ken (1998). „Retrospektywa: architektura masowo równoległego procesora” . Kontynuacja ISCA '98 25 lat międzynarodowych sympozjów na temat architektury komputerów . Isca '98: 15–16 . doi : 10.1145/285930.285937 . ISBN 978-1581130584 . S2CID 1875609 .

- JL Potter, wyd. (1986). Procesor masowo równoległy . [Sl]: Mit Press. ISBN 9780262661799 .

- Neil Boyd Coletti, „Przetwarzanie obrazu na macierzach podobnych do MPP”, Ph.D. praca magisterska, Wydział Informatyki, University of Illinois at Urbana-Champaign, 1983.

- Efstratios J. Gallopoulos; Scott D. McEwan (1983). Eksperymenty numeryczne z procesorem masowo równoległym . Wydział Informatyki Uniwersytetu Illinois w Urbana-Champaign . Źródło 11 czerwca 2012 r .

- Gallopoulos, EJ (lipiec 1985). „Masowo równoległy procesor do problemów w dynamice płynów”. Komunikacja w dziedzinie fizyki komputerowej . 37 (1–3): 311–315. Bibcode : 1985CoPhC..37..311G . doi : 10.1016/0010-4655(85)90167-5 .

- E. Gallopoulos, D. Kopetzky, SMcEwan, DL Slotnick i A. Spry, „Opracowywanie i symulacja programu MPP”. W „The Massively Parallel Processor”, red. JL Potter, s. 276–290, MIT Press, 1985

- Toma Henkla. „MPP przetwarza dane satelitarne; superkomputer twierdzi, że ma największą na świecie szybkość operacji we/wy”, Computerworld , 13 lutego 1984, s. 99.

- Erica J. Lernera. „Wiele procesorów ułatwia pracę”, Aerospace America , luty 1986, s. 50.

- ^ „Masowo równoległy procesor zapewnia dużą prędkość” . Tydzień lotnictwa i technologia kosmiczna . 1984-05-28. P. 157.

- Todd Kushner, Angela Wu, Azriel Rosenfeld, „Przetwarzanie obrazu w MPP”, rozpoznawanie wzorców - PR, tom. 15, nie. 3, s. 121–130, 1982